## フォワード・コンバータ用 オプトカプラ・ドライバ内蔵の 同期整流器コントローラ

## 特長

- 広い入力電源電圧範囲:3.7V~30V

- プリアクティブ・モード:

- パルス・トランス不要

- 軽負荷時のDCM動作

- 同期モード:

- 軽負荷時のFCM動作またはDCM動作

- 最も高い効率を実現

- 1.5% 精度の帰還電圧リファレンス

- 10mAオプトカプラ・ドライバ

- 出力パワーグッド・インジケータ

- ソフトスタート機能内蔵

## アプリケーション

- オフラインおよびハイブリッド車用バッテリの絶縁型電源

- 48V 絶縁型電源

- 産業用、自動車用、および軍用システム

## 概要

LT®8311はフォワード・コンバータの2次側で使用され、同期整流式MOSFET制御および出力電圧帰還をオプトカプラを介して実現します。LT8311独自のプリアクティブ・モードにより、1次側と2次側の間の通信に従来のパルス・トランスを使用する必要なく2次側のMOSFETを制御できます。プリアクティブ・モードでは、軽負荷時に出力インダクタ電流が不連続導通モード(DCM)で動作します。軽負荷時に強制連続モード(FCM)動作が望ましい場合、LT8311は代わりに同期モードで使用できます。このモードでは、1次側のICからLT8311へ同期制御信号を送信するためにパルス・トランスが必要です。

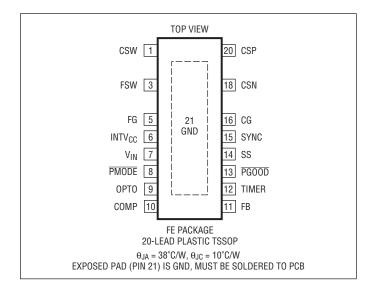

LT8311は機能満載のオプトカプラ・コントローラを備えており、1.5%精度のリファレンス、相互コンダクタンス・エラーアンプ、および10mAオプトドライバを内蔵しています。パワーグッド・モニタや出力ソフトスタート/オーバーシュート制御回路も内蔵しています。LT8311は、ピンが欠損している16ピンのFEパッケージで供給されており、高電圧のピン間隔要件に対応しています。

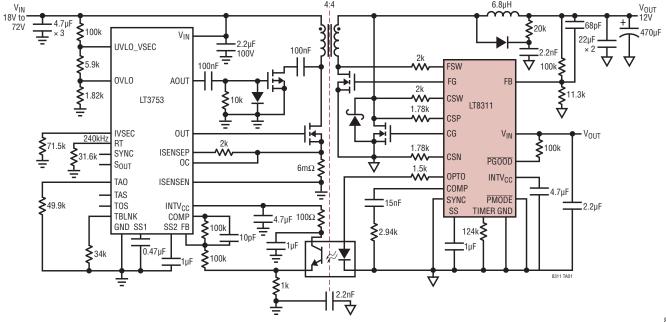

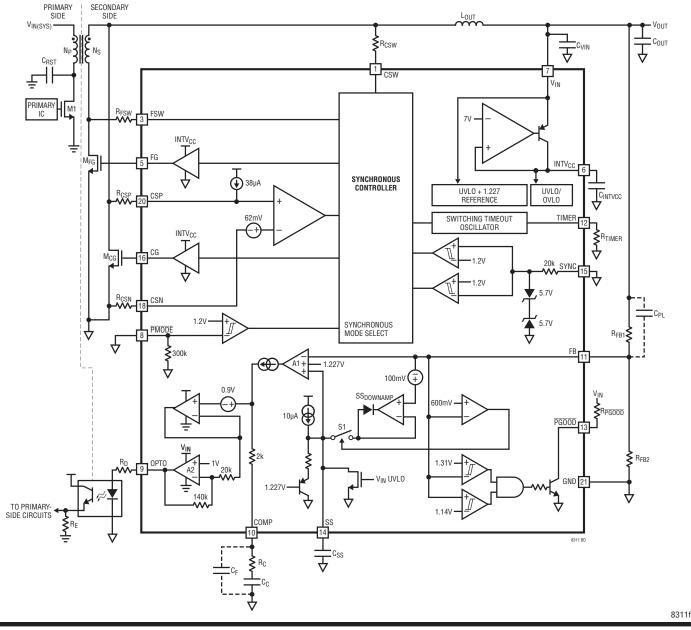

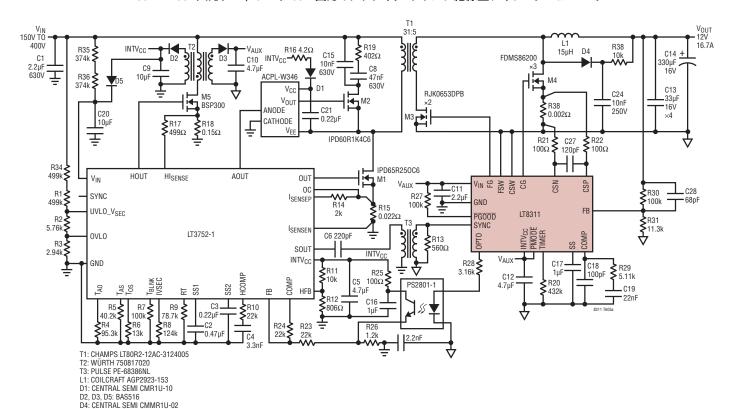

## 標準的応用例

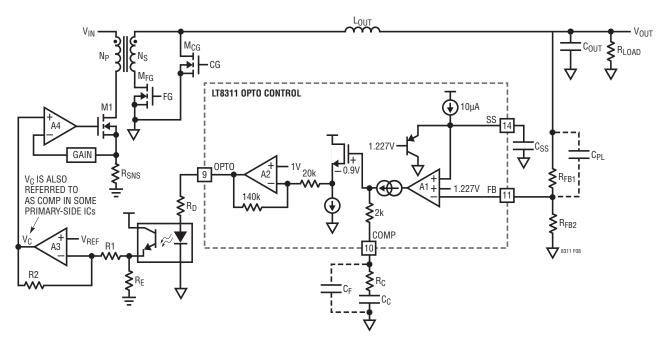

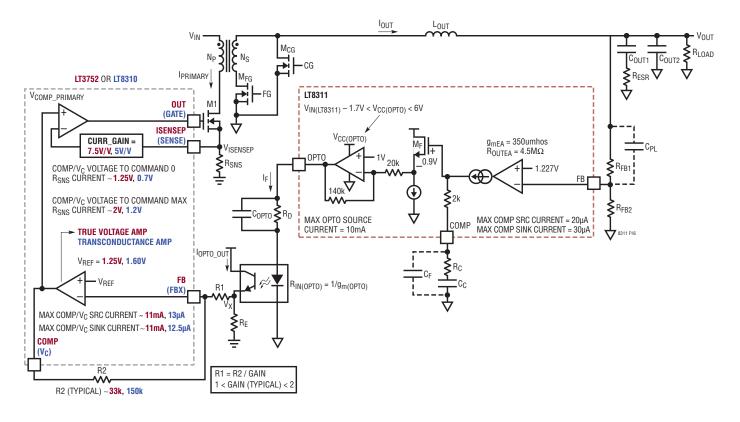

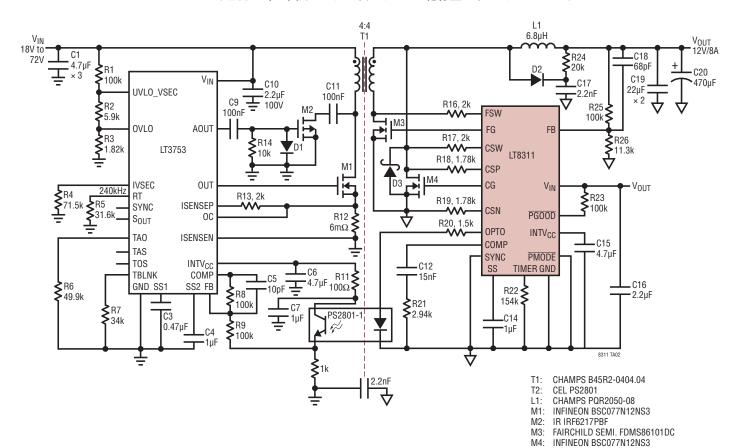

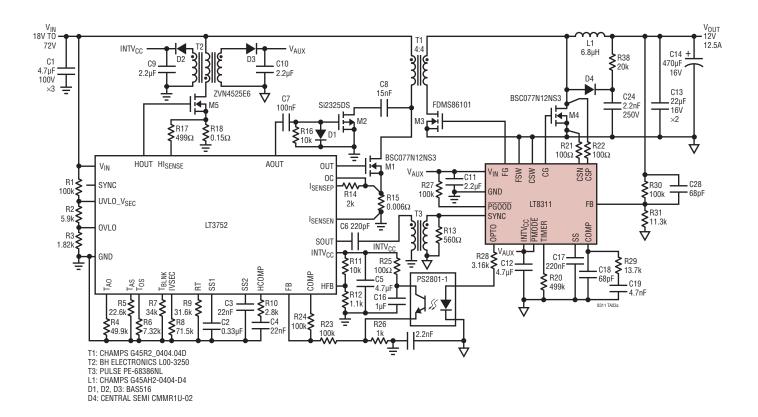

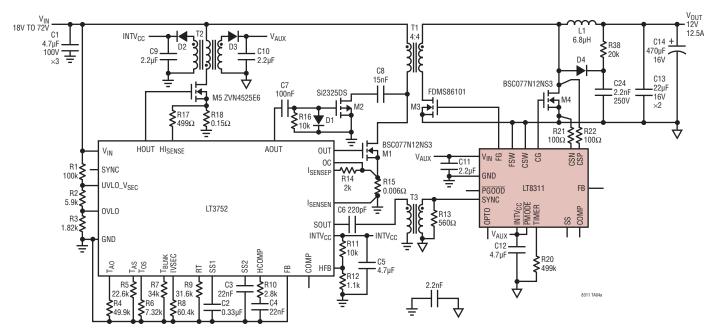

## 18V~72V入力、12V/8A出力のアクティブ・クランプ絶縁型フォワード・コンバータ

T LINEAR

# LT8311

# 目次

| 特長                         | 1  |

|----------------------------|----|

| アプリケーション                   | 1  |

| 標準的応用例                     | 1  |

| 概要                         | 1  |

| 絶対最大定格                     | 3  |

| 発注情報                       | 3  |

| ピン配置                       | 3  |

| 電気的特性                      | 4  |

| 標準的性能特性                    | 7  |

| ピン機能                       | 11 |

| ブロック図                      | 12 |

| 動作                         | 13 |

| CCM でのフォワード・コンバータ動作の基本     | 13 |

| LT8311の同期制御方式              | 17 |

| プリアクティブ・モードの同期制御           | 17 |

| 同期モードの同期制御                 |    |

| オプトカプラの制御                  | 21 |

| アプリケーション情報                 | 25 |

| V <sub>IN</sub> のバイアス電源    | 25 |

| INTV <sub>CC</sub> のバイアス電源 | 26 |

| LT8311のオプトカプラ制御の基本         | 27 |

| LT8311の同期制御の基本             | 31 |

| プリアクティブ・モードの同期制御           | 37 |

| 同期モードの同期制御                 | 38 |

| 標準的応用例                     | 40 |

| パッケージ                      | 47 |

| 標準的応用例                     | 48 |

| 関連製品                       | 48 |

## 絶対最大定格

## (Note 1)

| CSW、FSW、CSP                | 0.3V ∼ 150V   |

|----------------------------|---------------|

| SYNC                       | 12V~12V       |

| V <sub>IN</sub> , PGOOD    | 0.3V~30V      |

| INTV <sub>CC</sub> , PMODE | 0.3V ∼ 18V    |

| FB、SS、COMP                 | 0.3V ~ 2.5V   |

| TIMER                      | 0.3V ~ 1.5V   |

| CSN                        | 0.3V ~ 0.4V   |

| OPTO、TIMERの短絡電流期間          | 不定(Note 5)    |

| 動作接合部温度範囲                  |               |

| LT8311E (Note 2, 3)        | −40°C ~ 125°C |

| LT8311I (Note 2, 3)        | 40°C ∼ 125°C  |

| LT8311H (Note 2, 3)        | −40°C ~ 150°C |

| LT8311MP(Note 2, 3)        | −55°C ~ 150°C |

| 保存温度範囲                     | −65°C ~ 150°C |

| リード温度(半田付け、10秒)            | 300°C         |

|                            |               |

## ピン配置

## 発注情報

| 無鉛仕上げ          | テープアンドリール        | 製品マーキング* | パッケージ                 | 温度範囲           |

|----------------|------------------|----------|-----------------------|----------------|

| LT8311EFE#PBF  | LT8311EFE#TRPBF  | LT8311FE | 20-Lead Plastic TSSOP | -40°C to 125°C |

| LT8311IFE#PBF  | LT8311IFE#TRPBF  | LT8311FE | 20-Lead Plastic TSSOP | -40°C to 125°C |

| LT8311HFE#PBF  | LT8311HFE#TRPBF  | LT8311FE | 20-Lead Plastic TSSOP | -40°C to 150°C |

| LT8311MPFE#PBF | LT8311MPFE#TRPBF | LT8311FE | 20-Lead Plastic TSSOP | −55°C to 150°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\*温度グレードは出荷時のコンテナのラベルで識別されます。

無鉛仕上げの製品マーキングの詳細については、http://www.linear-tech.co.jp/leadfree/をご覧ください。

## 電気的特性

● は全動作温度範囲での規格値を意味する。それ以外はT<sub>A</sub> = 25°Cでの値。注記がない限り、V<sub>IN</sub> = 12V、V<sub>INTVCC</sub> = 8V、<del>PMODE</del> = 5V、C<sub>CG</sub> = C<sub>FG</sub> = 100pF。(Note 2)

| PARAMETER                                      | CONDITIONS                                                                                                                                                                                 |   | MIN   | ТҮР        | MAX        | UNITS   |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|------------|------------|---------|

| 電源                                             |                                                                                                                                                                                            |   |       |            |            |         |

| V <sub>IN</sub> Operating Range                |                                                                                                                                                                                            | • | 3.7   |            | 30         | V       |

| V <sub>IN</sub> UVLO                           | V <sub>IN</sub> Rising<br>Hysteresis                                                                                                                                                       | • | 50    | 3.6<br>100 | 3.7<br>150 | V<br>mV |

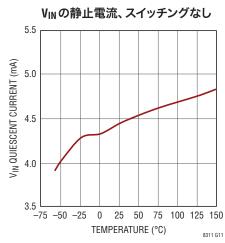

| Quiescent Current                              | Not Switching                                                                                                                                                                              |   |       | 4.5        | 5.5        | mA      |

| エラーアンプ                                         |                                                                                                                                                                                            |   |       |            |            |         |

| Feedback Reference Voltage                     | V <sub>IN</sub> = 12V                                                                                                                                                                      | • | 1.209 | 1.227      | 1.245      | V       |

| Feedback Voltage Line Regulation               | $3.7V \le V_{IN} \le 30V$ , % of FB Ref Voltage                                                                                                                                            |   |       | 0.015      | 0.1        | %       |

| Feedback Voltage Load Regulation               | 1.3V ≤ COMP ≤ 1.8V, % of FB Ref Voltage                                                                                                                                                    |   |       | 0.05       | 0.1        | %       |

| Feedback Pin Bias Current                      | Current Out of FB pin                                                                                                                                                                      |   |       | 120        | 200        | nA      |

| Error Amplifier Transconductance               | 1.3V ≤ COMP ≤ 1.8V                                                                                                                                                                         |   |       | 370        |            | μmhos   |

| Error Amplifier Voltage Gain                   | 1.3V ≤ COMP ≤ 1.8V                                                                                                                                                                         |   |       | 65         |            | dB      |

| Error Amplifier Output Swing High              | FB = 1V                                                                                                                                                                                    |   | 1.9   | 2.3        | 2.8        | V       |

| Error Amplifier Output Swing Low               | FB = 1.5V                                                                                                                                                                                  |   | 0.75  | 1          | 1.25       | V       |

| パワーグッド                                         |                                                                                                                                                                                            |   |       |            |            |         |

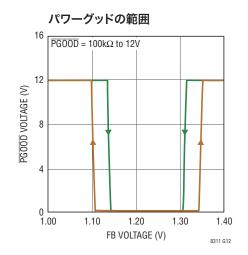

| Power NOT Good (Outside This Window)           | % Relative to FB Ref Voltage                                                                                                                                                               |   | ±4    | ±10        | ±16        | %       |

| Power Good (Inside This Window)                | % Relative to FB Ref Voltage                                                                                                                                                               |   |       | ±7         |            | %       |

| Power Good Indicator Wait Time                 | Minimum Time That FB Must Stay within Power Good Window Before PGOOD Pin Goes Low                                                                                                          |   |       | 175        |            | μs      |

| Power Good Leakage                             | <u>PGOOD</u> = 30V                                                                                                                                                                         |   |       |            | ±1         | μА      |

| Power Good Output Low Voltage                  | Current into PGOOD Pin = 1mA                                                                                                                                                               | • |       | 0.2        | 0.3        | V       |

| ソフトスタート(SS)                                    |                                                                                                                                                                                            |   |       |            |            |         |

| SS Wake-Up Slew Current                        | Current Exists Upon Part Wake Up, Shuts Off After SS Wake Up<br>Offset Voltage Is Satisfied (Note 6)                                                                                       |   |       | 1          |            | mA      |

| SS Wake-Up Offset Voltage                      | V <sub>FB</sub> – V <sub>SS</sub> , Upon Part Wake Up SS Is Slewed Up to an Offset Voltage<br>Below FB by SS Wake-Up Slew Current                                                          |   |       | 16         |            | mV      |

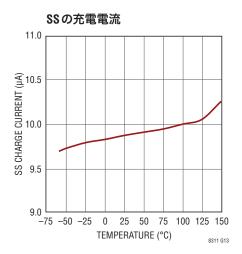

| SS Charge Current                              | SS = 0V, FB = 0.6V (Note 9)                                                                                                                                                                | • | 9     | 10         | 11         | μА      |

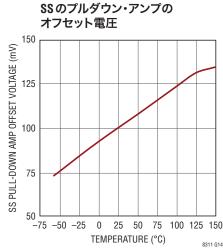

| SS Pull-Down Amplifier Offset Voltage          | V <sub>SS</sub> – V <sub>FB</sub> , Pull-Down Amplifier Prevents SS from Rising Beyond<br>This Offset Voltage Above FB When the FB Pin Voltage Is Below 50%<br>of the FB Reference Voltage |   |       | 100        |            | mV      |

| SS Pull-Down Amplifier Maximum<br>Sink Current | SS = 1.5V, FB = 0.6V (Note 7)                                                                                                                                                              |   |       | 13         |            | mA      |

| SS High Clamp Voltage                          |                                                                                                                                                                                            |   | 1.8   | 2          |            | V       |

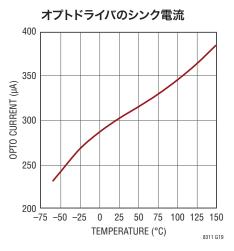

| オプト・ドライバ                                       |                                                                                                                                                                                            |   |       |            |            |         |

| COMP Buffer Input Offset Voltage               | 1.3V ≤ COMP (Note 5)                                                                                                                                                                       |   |       | 0.9        |            | V       |

| Opto-Driver Reference Voltage                  | (Note 5)                                                                                                                                                                                   |   |       | 1          |            | V       |

| Opto-Driver DC Gain                            | (Note 5)                                                                                                                                                                                   |   |       | -7         |            | V/V     |

|                                                |                                                                                                                                                                                            |   |       |            |            |         |

## 電気的特性

● は全動作温度範囲での規格値を意味する。それ以外はT<sub>A</sub> = 25°Cでの値。注記がない限り、V<sub>IN</sub> = 12V、V<sub>INTVCC</sub> = 8V、<del>PMODE</del> = 5V、C<sub>CG</sub> = C<sub>FG</sub> = 100pF。(Note 2)

| PARAMETER                                              | CONDITIONS                                                                    |   | MIN                       | TYP                   | MAX  | UNITS   |

|--------------------------------------------------------|-------------------------------------------------------------------------------|---|---------------------------|-----------------------|------|---------|

| Inverting DC Gain From COMP Pin to                     | $(\Delta V_{OPTO}/\Delta V_{COMP})$ , 1.290V $\leq COMP \leq 1.310V$          |   |                           | -5                    |      | V/V     |

| OPTO Pin                                               | $(\Delta V_{OPTO}/\Delta V_{COMP})$ , $1.490V \le COMP \le 1.510V$            |   |                           | -5.9                  |      | V/V     |

|                                                        | $(\Delta V_{OPTO}/\Delta V_{COMP})$ , $1.890V \le COMP \le 1.910V$            |   |                           | -6.2                  |      | V/V     |

| Opto-Driver –3dB Bandwidth                             | No Load (Note 5)                                                              |   |                           | 400                   |      | kHz     |

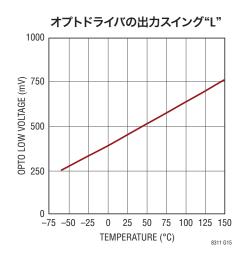

| Opto-Driver Output Swing Low                           | FB = 1V, COMP = SS = OPTO = Open                                              | • |                           | 0.5                   | 0.85 | V       |

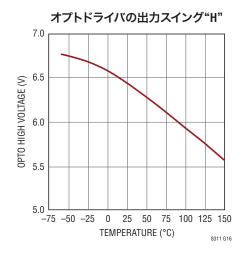

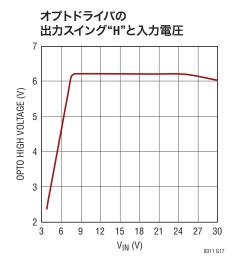

| Opto-Driver Output Swing High                          | V <sub>IN</sub> = 3.7V, FB = 1.5V, COMP = SS = Open, I <sub>OPTO</sub> = 10mA | • | V <sub>IN</sub> – 1.7     | V <sub>IN</sub> – 1.4 |      | V       |

|                                                        | V <sub>IN</sub> = 30V, FB = 1.5V, COMP = SS = Open, I <sub>OPTO</sub> = 10mA  | • | 5.2                       | 6.5                   |      | V       |

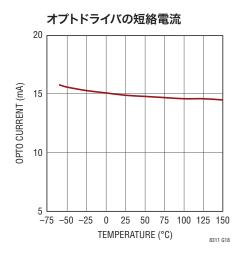

| Opto-Driver Output Short-Circuit Current               | V <sub>IN</sub> = 30V, FB = 1.5V, COMP = SS = Open, OPTO = 0V (Note 6)        | • | 10.5                      | 15                    | 18   | mA      |

| Opto-Driver Output Sink Current                        | FB = 1V, OPTO = 1.2V (Note 7)                                                 | • | 200                       | 300                   | 420  | μА      |

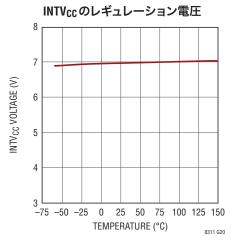

| 内部リニア・レギュレータ                                           |                                                                               | • |                           |                       |      |         |

| INTV <sub>CC</sub> Regulation Voltage                  | No Load                                                                       | • | 6.5                       | 7                     | 7.5  | V       |

| INTV <sub>CC</sub> Load Regulation                     | $(\Delta V_{INTVCC}/\Delta I_{INTVCC}), 0A \le I_{INTVCC} \le 20mA$           |   |                           | 1.8                   | 3    | mV/mA   |

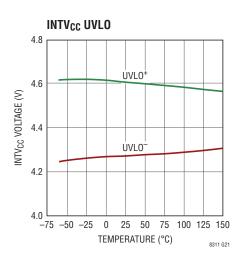

| INTV <sub>CC</sub> UVLO Rising                         |                                                                               | • |                           | 4.6                   | 4.8  | V       |

| INTV <sub>CC</sub> UVLO Falling                        |                                                                               | • | 4.1                       | 4.3                   |      | V       |

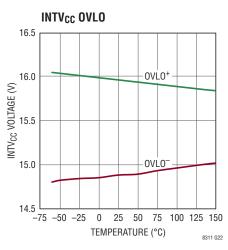

| INTV <sub>CC</sub> OVLO Rising                         |                                                                               | • |                           | 16.5                  | 17.5 | V       |

| INTV <sub>CC</sub> OVLO Falling                        |                                                                               | • | 14                        | 15                    |      | V       |

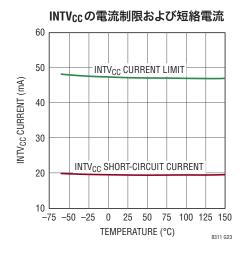

| INTV <sub>CC</sub> Current Limit                       | INTV <sub>CC</sub> > I <sub>INTVCC_UVLO_RISING</sub> (= 4.6V)                 | • | 38                        | 48                    | 58   | mA      |

|                                                        | INTV <sub>CC</sub> < I <sub>INTVCC_UVLO_FALLING</sub> (= 4.3V)                |   |                           | 20                    |      | mA      |

| INTV <sub>CC</sub> Dropout Voltage                     | V <sub>IN</sub> = 6V, I <sub>INTVCC</sub> = 10mA, Not Switching               |   |                           | 400                   |      | mV      |

| CGとFGのゲート・ドライバ                                         |                                                                               | ' |                           |                       |      |         |

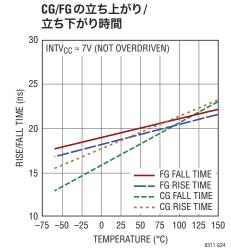

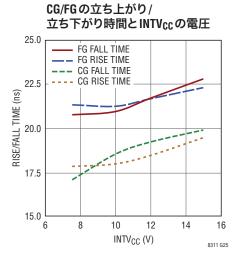

| Driver Output Rise Time                                | $C_{CG} = C_{FG} = 3.3 \text{nF}, \text{INTV}_{CC} = 8 \text{V (Note 4)}$     |   |                           | 25                    |      | ns      |

| Driver Output Fall Time                                | C <sub>CG</sub> = C <sub>FG</sub> = 3.3nF, INTV <sub>CC</sub> = 8V (Note 4)   |   |                           | 25                    |      | ns      |

| Driver Output High Voltage                             |                                                                               | • | V <sub>INTVCC</sub> – 0.2 |                       |      | V       |

| Driver Output Low Voltage                              |                                                                               | • |                           |                       | 0.7  | V       |

| PMODE の選択                                              |                                                                               |   |                           |                       |      |         |

| PMODE Trip Voltage                                     | PMODE Ramp Up<br>Hysteresis                                                   | • | 1                         | 1.2<br>30             | 1.4  | V<br>mV |

| PMODE Input Current                                    | PMODE = 18V                                                                   | • |                           | 60                    | 90   | μА      |

| プリアクティブ・モード(PMODEをOVに                                  | 妾続)                                                                           |   |                           |                       |      |         |

| Preactive Mode Operating Frequency Range               |                                                                               | • | 100                       |                       | 300  | kHz     |

| CSW High Trip Voltage                                  | CSW Ramp Up                                                                   | • | 1                         | 1.2                   | 1.4  | V       |

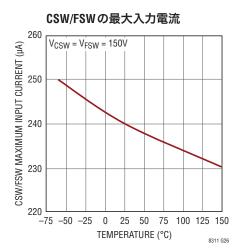

| CSW High Input Current                                 | CSW = 150V (Note 7)                                                           | • |                           | 250                   | 500  | μА      |

| CSW Low Trip Voltage                                   | CSW Ramp Down                                                                 | • | -250                      | -150                  | -50  | mV      |

| FSW Trip Voltage                                       |                                                                               | • | 1                         | 1.2                   | 1.4  | V       |

| FSW High Input Current                                 | FSW = 150V (Note 7)                                                           | • |                           | 250                   | 500  | μА      |

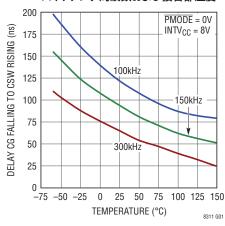

| CG Falling Edge to CSW Rising Edge<br>Prediction Delay | CSW = 150kHz (Note 10), FSW = 0V, CSP = -500mV                                | • | 5                         | 100                   | 300  | ns      |

| CG Falling Edge Delay to FG Rising Edge                | CSW = 150kHz (Note 10), FSW = 0V, CSP = -500mV                                | • | 10                        | 50                    | 80   | ns      |

|                                                        |                                                                               |   |                           |                       |      |         |

## 電気的特性

● は全動作温度範囲での規格値を意味する。それ以外は T<sub>A</sub> = 25°C での値。注記がない限り、V<sub>IN</sub> = 12V、V<sub>INTVCC</sub> = 8V、<del>PMODE</del> = 5V、 C<sub>CG</sub> = C<sub>FG</sub> = 100pF。(Note 2)

| PARAMETER                                       | CONDITIONS                                                                                                                                                                                                                             |   | MIN              | TYP                    | MAX               | UNITS                   |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------------|------------------------|-------------------|-------------------------|

| 同期モード(PMODEをINTV <sub>CC</sub> に接続)             |                                                                                                                                                                                                                                        |   |                  |                        |                   |                         |

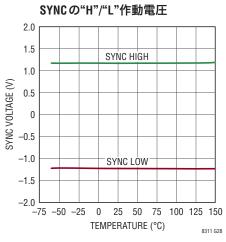

| SYNC High Trip Voltage                          | SYNC Ramp Up<br>Hysteresis                                                                                                                                                                                                             | • | 0.9              | 1.2<br>-2.4            | 1.5               | V                       |

| SYNC Low Trip Voltage                           | SYNC Ramp Down<br>Hysteresis                                                                                                                                                                                                           | • | -1.5             | -1.2<br>2.4            | -0.9              | V                       |

| SYNC Minimum Pulse Width                        | SYNC = 0V to ±2V Pulse<br>SYNC = 0V to ±6V Pulse (Note 5)                                                                                                                                                                              | • |                  | 40<br>20               | 100               | ns<br>ns                |

| SYNC Input Current                              | -3.5V < SYNC < 3.5V<br>SYNC = ±10V (Note 6, 7)                                                                                                                                                                                         | • |                  | 300                    | ±1<br>400         | μΑ<br>μΑ                |

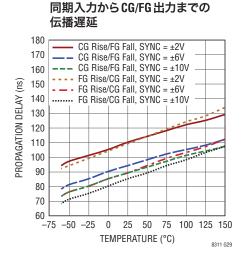

| SYNC Propagation Delay To CG/FG<br>Outputs      | SYNC Rising Edge (OV to 2V) to CG Rising Edge (Note 8) SYNC Rising Edge (OV to 6V) to CG Rising Edge (Notes 5, 8) SYNC Falling Edge (OV to 2V) to FG Rising Edge (Note 8) SYNC Falling Edge (OV to 6V) to FG Rising Edge (Notes 5, 8), | • |                  | 100<br>75<br>100<br>85 | 150<br>150        | ns<br>ns<br>ns          |

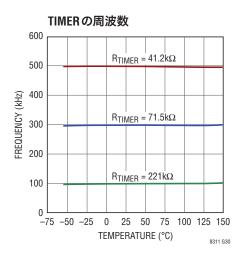

| TIMER Timeout Frequency                         | C <sub>CG</sub> = C <sub>FG</sub> = 3.3nF<br>R <sub>TIMER</sub> = 41.2k<br>R <sub>TIMER</sub> = 71.5k<br>R <sub>TIMER</sub> = 221k                                                                                                     | • | 425<br>255<br>80 | 505<br>300<br>100      | 585<br>345<br>120 | ns<br>kHz<br>kHz<br>kHz |

| TIMER Short-Circuit Current                     | TIMER = 0V                                                                                                                                                                                                                             | • |                  | 40                     | 60                | μA                      |

| 電流コンパレータ                                        |                                                                                                                                                                                                                                        |   | ,                |                        |                   |                         |

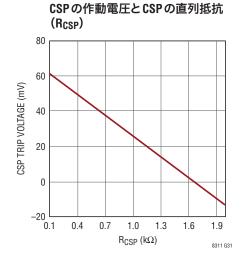

| Current Comparator Trip Threshold               | CSP Ramp Up, $R_{CSP} = R_{CSN} = 0\Omega$                                                                                                                                                                                             | • | 48               | 62                     | 72                | mV                      |

|                                                 | CSP Ramp Up, $R_{CSP} = R_{CSN} = 1.62k\Omega$ (Note 5)                                                                                                                                                                                |   |                  | 0                      |                   | mV                      |

| Current Comparator Blank Time in Preactive Mode | From Rising CG Edge Until Blanking Ends (Note 5)                                                                                                                                                                                       |   |                  | 250                    |                   | ns                      |

| Current Comparator Blank Time in SYNC Mode      | From Rising CG Edge Until Blanking Ends                                                                                                                                                                                                |   |                  | 400                    |                   | ns                      |

| CSP Current at Low CSP Voltage                  | CSP = 0V (Note 6)                                                                                                                                                                                                                      | • | 30               | 38                     | 50                | μА                      |

| CSP Current at High CSP Voltage                 | CSP = 150V (Note 7)                                                                                                                                                                                                                    | • |                  | 200                    | 500               | μА                      |

| CSN Current                                     | CSN = 0V (Note 6)                                                                                                                                                                                                                      | • |                  | 0.1                    | 1                 | μА                      |

Note 1: 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

Note 2: LT8311はT」がTAにほぼ等しいパルス負荷条件でテストされる。LT8311Eは、 $0^{\circ}$ C~125°Cの接合部温度で仕様に適合することが保証されている。 $-40^{\circ}$ C~125°Cの動作接合部温度での仕様は、設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LT8311Iは $-40^{\circ}$ C~125°Cの動作接合部温度範囲で保証されている。LT8311Hは $-40^{\circ}$ C~150°Cの動作接合部温度範囲で保証されている。LT8311MPは $-55^{\circ}$ C~150°Cの動作接合部温度範囲で保証されている。ET831MPは $-55^{\circ}$ C~150°Cの動作接合部温度範囲で保証されている。高い接合部温度範囲で保証されている。125°Cを超える接合部温度では動作寿命はディレーティングされる。

Note 3: LT8311 には、短時間の過負荷状態の間デパイスを保護するための過熱保護機能が備わっている。過熱保護が動作しているとき、接合部温度は最大動作接合部温度を超える。規定された最大動作接合部温度を超えた状態で動作が継続すると、デパイスの信頼性を損なう恐れがある。

Note 4: 立ち上がり時間および立ち下がり時間は信号エッジの10%と90%の2点間で測定される。

Note 5: 設計か、静的テストとの相関によって保証されている。

Note 6:電流はピンから流れ出す。

Note 7:電流はピンに流れ込む。

Note 8:伝播遅延は、目的とする2つの信号エッジの50%の2点間で測定される。

Note 9: SS 充電電流とは、LT8311の起動時に一定の条件が満たされた後にSSピンから流れる電流を指す(図9に示す「起動時のオプトカプラ制御動作」のフローチャートを参照)。

Note 10:CSW は  $V_{HIGH}$  = 7V および  $V_{LOW}$  = -0.7V の矩形波 (デューティ・サイクル = 50%)。

LINEAR TECHNOLOGY

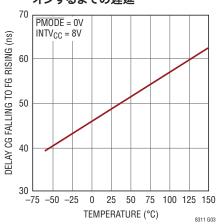

CGがオフしてからCSWの立ち上がり エッジまでの遅延とCSWの スイッチング周波数および接合部温度

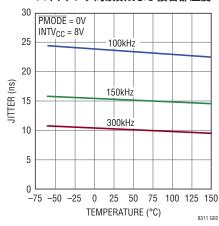

CGがオフしてからCSWの立ち上がり エッジまでの遅延でのジッタとCSWの スイッチング周波数および接合部温度

CGがオフしてからFGが オンするまでの遅延

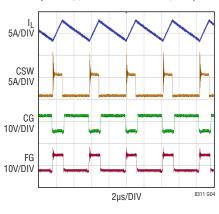

プリアクティブ方式の波形 (アクティブ・クランプのリセット、CCM)

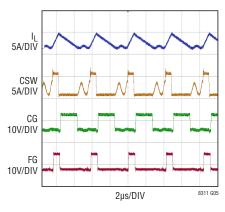

プリアクティブ方式の波形 (アクティブ・クランプのリセット、軽いDCM)

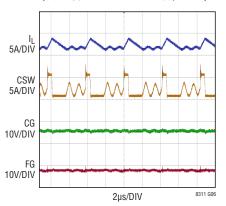

プリアクティブ方式の波形 (アクティブ・クランプのリセット、深いDCM)

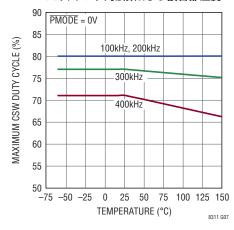

CSWの最大デューティ・サイクルの ディレーティング曲線とCSWの スイッチング周波数および接合部温度

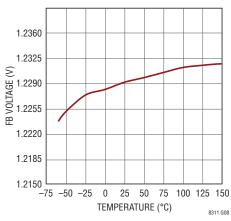

帰還リファレンス電圧

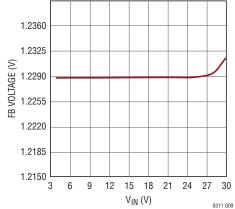

帰還リファレンス電圧とVIN

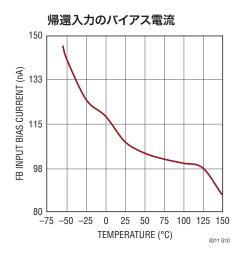

INFAD

8311f

TECHNOLOGY TECHNOLOGY

$\mathcal{C}$

## ピン機能

**CSW(ピン1)**:キャッチMOSFETのドレイン検出ピン。プリアクティブ・モードでは、このピンを2kの抵抗(標準)を介して外付けのNチャネル・キャッチMOSFETのドレインに接続します。このピンの寄生容量は最小限に抑えてください。同期モードではGNDに接続します。

FSW(ピン3):フォワードMOSFETのドレイン検出ピン。プリアクティブ・モードでは、このピンを2kの抵抗(標準)を介して外付けのNチャネル・フォワードMOSFETのドレインに接続します。このピンの寄生容量は最小限に抑えてください。同期モードではGNDに接続します。

**FG (ピン5)**: フォワード MOSFET のゲート・ドライバ・ピン。このピンは外付けのNチャネル・フォワード MOSFET のゲートを駆動します。このピンとフォワード MOSFET ゲートの間のトレース長は最小限に抑えてください。

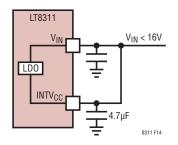

INTV<sub>CC</sub>(ピン6): 内部リニア・レギュレータの出力ピン。INTV<sub>CC</sub>は、LT8311のゲート・ドライバに電力を供給します。このピンの電圧は内部で7Vに安定化されています。あるいは、このピンを外部でオーバードライブしてもかまいません。このピンとGNDの間に4.7 $\mu$ F以上(セラミック・コンデンサ)を接続する必要があります。

**V<sub>IN</sub> (ピン7)**: 入力電源ピン。このピンはすぐ近くでバイパスする必要があります。

**PMODE** (ピン8): プリアクティブ・モード選択ピン。 PMODEを GNDに接続すると、プリアクティブ・モードが有効になります。 PMODEをINTV<sub>CC</sub>に接続すると、同期モードが有効になります。

**OPTO (ピン9)**: オプトカプラ・ドライバの出力ピン。このピンは 直列抵抗を介してオプトカプラの入力に接続します。このピン は、ソース電流が最大10mA、シンク電流が標準300μAで、 短絡保護されています。

**COMP (ピン10)**: エラーアンプの出力ピン。LT8311のトランスコンダクタンス・エラーアンプを電圧帰還ループの一部として使用する場合は、このピンに外付けの補償回路網を接続します。

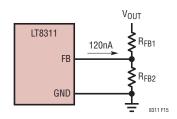

FB(ピン11): 帰還ピン。これはLT8311の内部エラーアンプの反転入力です。FBピンの電圧は、1.227Vの内部リファレンスとSSピンの電圧のうち低い方を追跡します。このピンからは、通常は75nA (バイアス電流)が流れ出します。目的の出力電圧を設定するには、このピンを出力からの抵抗分割器回路網に接続します。

TIMER (ピン12): スイッチング周期のタイムアウト・ピン。このピンとグランドの間に抵抗を接続することにより、(2つの MOSFETのオン時間の間のデッドタイムを含む)フォワード MOSFETとキャッチ MOSFET のオン時間の合計について、す

べてのサイクルで上限が設定されます。キャッチMOSFETおよびフォワードMOSFETのオン時間の合計が、(デッドタイムを含む)サイクルごとに、TIMERピンの抵抗で設定されたタイムアウト期間を超えると、同期式の導通はすべて停止します。タイムアウト期間が再度リセットされると、同期式の導通が再開されます。TIMER抵抗のプログラミングの詳細については、「アプリケーション情報」のセクションを参照してください。このピンのグランド帰路トレースは短くして、スイッチング・ノイズがある経路から遠ざけるようにしてください。

**PGOOD**(ピン13): 出力パワーグッド・ピン。FBピンの電圧が、1.227Vの内部リファレンスの $\pm 7\%$ の範囲内に $175\mu$ sの間とどまると、オープンドレイン出力はグランド電位に低下します。内部のPGOODコンパレータには $\pm 3\%$ のヒステリシスがあります。したがって、FBの電圧が1.227Vリファレンスの $\pm 10\%$ の範囲から外れると、PGOODピンは外付けのプルアップ抵抗または電流源によって"H"になります。

SS(ピン14): ソフトスタート・ピン。SSピンとGNDの間のコンデンサは、内部で調整されたSSピンの10µA電流源によって充電されます。FBピンの電圧はSSピンの電圧と1.227Vの内部リファレンスのうち低い方を追跡するので、SSピンの充電速度を利用して、FBピンの電圧がそのレギュレーション電圧である1.227Vまで充電されるスルーレートを設定できます。SSピンは標準では2Vまで充電されます。LT8311を電圧帰還ループの一部として使用する場合は、このピンとGNDの間に1nF以上のセラミック・コンデンサを配置します。SSピンの起動およびオーバーシュート制御機能の詳細については、「アプリケーション情報」のセクションを参照してください。

SYNC (ピン15): 同期ピン。SYNCピンは、同期モードでのみ使用され、同期スイッチングのタイミング情報を受信するエッジ感度の高い入力として機能します。このピンは、通常はパルス・トランスを介して1次側のICから送られたPWM同期信号によって駆動されます。SYNCピンに負電圧(しきい値は-1.2V)を通過させると、フォワードMOSFETがオンになり、キャッチMOSFETがオフになります。同様に、正電圧(しきい値は1.2V)を通過させると、キャッチMOSFETがオンになり、フォワードMOSFETがオフになります。プリアクティブ・モードでは、SYNCピンをGNDに接続してください。

**CG(ピン16)**:キャッチMOSFETのゲート・ドライバ・ピン。このピンは外付けのNチャネル・キャッチMOSFETのゲートを駆動します。このピンとキャッチMOSFETゲートの間のトレース長は最小限に抑えてください。

CSN、CSP(ピン18/ピン20):電流検出差動入力。CSPとCSNは、それぞれLT8311の内部電流検出コンパレータの正入力および負入力です。これらのピンは、通常はキャッチMOSFET

## ピン機能

の両端に接続して、VDSによる電流検出を実行します。あるいは、より高精度の電流検出機構が望ましい場合は、キャッチMOSFETのソースでの検出抵抗の両端にこれらのピンを接続できます。電流コンパレータは標準62mVで作動します。CSPピンのソース電流は38µAなので、CSPピンと直列に抵抗を配置することにより、62mVより小さい作動電圧を設定できます。電流コンパレータの入力バイアス電流(100nA)によって発生する電圧オフセットと釣り合うように、同一の抵抗をCSN

ピンと直列に配置することを推奨します。プリアクティブ・モードでは、キャッチ MOSFET のソースからドレインへの電流が0または正の値で作動するようにCSPピンとCSNピンを構成する必要があります(プリアクティブ・モードでは、キャッチMOSFET での電流がドレインからソースへ流れることはできません)。

**GND(露出パッド・ピン21)**: グランド。露出パッドはローカル・グランド・プレーンに直接半田付けする必要があります。

## ブロック図

LINEAR

12

LT8311は、フォワード・コンバータの2次側にある同期 MOSFETとオプトカプラを制御します。R<sub>DS(ON)</sub>の低い MOSFETを同期制御すると、通常はフォワード・コンバータでの電力損失が少なくなることにつながります。電力損失が少なくなるとコンバータの効率が向上するので、入力電源の要件を緩和してある程度の出力電力をサポートすることにより、長期的なコスト節減をもたらすことができます。また、効率が向上することにより、整流器内で発生した熱を放散するのに必要なヒートシンクのサイズを抑えることもできます。その結果、動作周囲温度範囲が広がるので、多くの産業用アプリケーションで役立つ可能性があります。

LT8311は、オプトカプラ制御により、入力と負荷の全範囲で高精度の出力電圧レギュレーションも実現します。LT8311のオプトカプラ制御回路は、電源投入時および出力短絡回復時に堅牢なトランジェント応答を保証する、起動と定常状態の機能も多数内蔵しています。

#### CCM でのフォワード・コンバータ動作の基本

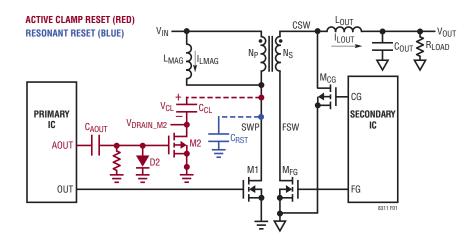

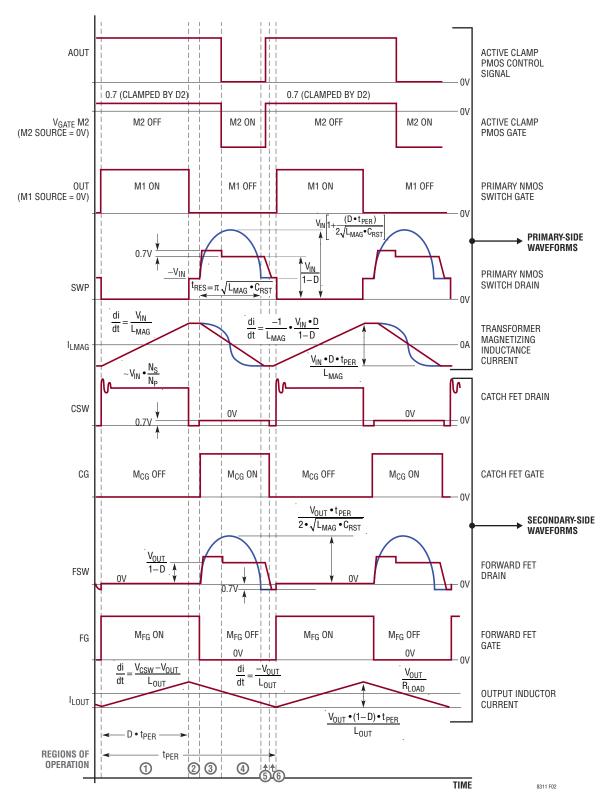

連続導通モード(CCM)で動作するフォワード・コンバータの タイミング図を図2に示します。タイミング図は6つの動作領域に分かれています。以下に示す各動作領域の説明については、図1および図2を参照してください。

#### 領域1(図2)

OUTが"H"になると、M1がオンします。 $M_{CG}$ がM1と相互に 導通しないように、OUTが"H"になる前からCGの電圧はOV になっている必要があります。LT8311のプリアクティブ・モード(後述)は、M1がオンする前に $M_{CG}$ をオフにする革新的な 方式です。FGはフォワードMOSFET ( $M_{FG}$ )をオンのまま維持するためこの期間中"H"になっている必要があります。そのため、出力インダクタ電流 ( $I_{LOUT}$ )が (トランスの2次巻線を介して)低インピーダンス経路を流れます。この段階では、トランスの磁気コア内に磁化電流 ( $I_{LMAG}$ )が発生し、 $V_{IN}$ からM1を通ってGNDに流れます。出力インダクタ電流 ( $I_{LOUT}$ )は、( $V_{CSW}$  –  $V_{OUT}$ )/ $I_{LOUT}$ の割合で増加します。

#### 領域2(図2)

OUTが"L"になってM1がオフすると、トランスは高インピーダンスになり、ILOUTの導通を停止します。出力インダクタを流れる電流は瞬時には0にならないので、この電流によってキャッチMOSFETのドレイン(CSW)はグランド電位に向かって低下します。最終的に、MCGのボディ・ダイオードにより、CSWはグランドよりダイオード1個分低い電圧にクランプされます。このボディ・ダイオードは、(従来の降圧コンバータでのキャッチ・ダイオードと同様)出力インダクタ電流を供給します。同様に、CSW電位の大幅な低下によってトランスの2次巻線電圧は小さくなります。トランスの動作によって1次巻線電圧も小さくなるので、SWPの電圧は実質的にVINに近づくことになります。

図1. アクティブ・クランプ・リセット(赤)または共振リセット(青)を備えたフォワード・コンバータ

図2. CCMでのアクティブ・クランプ・フォワード・コンバータのタイミング図。共振リセット波形を青で表示

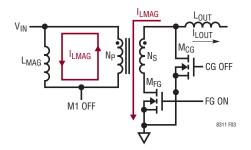

$M_{FG}$ はオンのままであり、 $M_{CG}$ のボディ・ダイオードもオンしているので、2次巻線電圧はダイオード1個分の電圧にクランプされます。トランスの動作によって、SWPの電圧はほぼ $V_{IN}$ と同じ電圧にクランプされます。図3に示すように、 $I_{LMAG}$ は2次巻線を流れ、 $M_{FG}$ のドレイン-ソース間を通ってグランドに流れます。 $M_{CG}$ のボディ・ダイオードは $I_{LOUT}$ および $I_{LMAG}$ を供給します。

#### 領域3(図2)

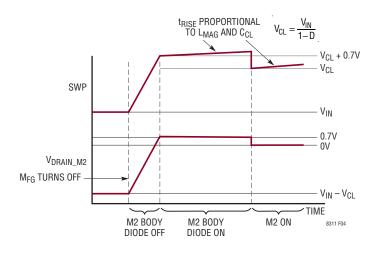

FGが"L"になると、トランスのリセット動作を開始できます。  $I_{LMAG}$ には、2次側の $M_{FG}$ を流れる低インピーダンス経路は存在しなくなりました。その結果、この電流は1次側に「急激に戻り」、1次側の共振コンデンサに流れ込みます。共振リセットでは、 $I_{LMAG}$ は $M_{FG}$ がオフになるとすぐに $C_{RST}$ に流れ込むので、SWPの電圧は $L_{MAG}$ および $C_{RST}$ によって設定され

た時定数により、準正弦波状に上昇します。アクティブ・クランプのリセット時には、 $M_{FG}$ がオフになると、 $I_{LMAG}$ によって最初はSWPの電圧が急速に立ち上がります。図2に示すように、 $I_{LMAG}$ は $M_{FG}$ がオフになっても、すぐにはPクティブ・クランプ・コンデンサに流れ込みません。 $C_{CL}$  両端の電圧( $=V_{CL}=V_{IN}/(1-D)$ )は、最初は $M_{2}$ のボディ・ダイオードを逆方向にバイアスしています。SWPの電圧が $M_{2}$ のボディ・ダイオードを順方向にバイアスするのに十分なほど高くなった場合に限り、 $I_{LMAG}$ は $C_{CL}$ に流れ始めます。この状況になるのは、SWPの電圧が $V_{CL}$ +0.7Vになったときです。この時点で、SWPの電圧は、 $L_{MAG}$ とPクティブ・クランプ・コンデンサによる時定数で決まる速度で上昇しますが、P0ティブ・クランプ・コンデンサは、通常は共振リセット・コンデンサよりはるかに大容量です。

図3. FGがオンの場合、M1がオフするとI<sub>LMAG</sub>は M<sub>FG</sub>を通って2次側のグランドへ流れる

図4. 図2のタイミング図から抜粋した領域3の詳細。 $M_{FG}$ がアクティブ・クランプ・リセット時にオフすると、 $I_{LMAG}$  によって最初は SWP の電圧が急速に上昇し、 $V_{IN}$  から  $V_{CL}+0.7V$  になる。 その時点で M2 のボディ・ダイオードがオンし、 $I_{LMAG}$  は  $C_{CL}$  に流れる

2つのリセット機構の最終的な目標は、SWPノードを $V_{IN}$ より高い電圧に上昇させ、ボルト秒の適切な制限値を $L_{MAG}$ に設定して、磁化電流をリセットできるようにすることです。磁気コアをサイクルごとにリセットすると、磁気コア内部での磁束増大を防止して、トランスが飽和しないようになります。FSWの電圧は、トランスのリセット中はSWPノードの電圧を追跡します。CGが"H"になると、 $I_{LOUT}$ は $M_{CG}$ のボディ・ダイオードによる導通から $M_{CG}$ 自体の導通に切り替わります。

#### 領域4(図2)

- 1. **アクティブ・クランプ・リセットの場合(赤の波形)**: AOUT が"L"になると、M2のゲート電位はデカップリング・コンデンサCAOUTによってグランドより低くなります。これにより、M2(アクティブ・クランプPMOS)がオンします。M2は I<sub>LMAG</sub>が負になる前にオンして、I<sub>LMAG</sub>がアクティブ・クランプ・コンデンサを通じた導通を持続して完全にリセットできるようにする必要があります。アクティブ・クランプ・リセットは領域4の終了までに完了し、I<sub>LMAG</sub>はリセットされて負の値になります。

- 2. 共振リセットの場合(青の波形): 共振リセットが最終的に 完了するのは、SWPの準正弦波波形が $V_{IN}$ に戻るときで、 そのときまでに $I_{LMAG}$ はリセットされて負の値になっていま す。FSW は、最終的には $M_{FG}$ のボディ・ダイオードによって クランプされ、 $I_{LMAG}$ を2次巻線を通じて出力インダクタの 方向に導通させます(図3の場合と同様ですが、 $I_{LMAG}$ の 方向は1次側と2次側が逆になります)。2次巻線の両端に

ダイオード1個分の電圧がかかると、トランスの動作によって(巻数比に比例した)同様の電圧が1次巻線に発生するので、SWPの電圧は $V_{\rm IN}$ にクランプされます。 $M_{\rm CG}$ は電流  $I_{\rm LOUT}$  –  $I_{\rm LMAG}$ を導通し続けます。

#### 領域5(図2)

アクティブ・クランプ・リセットの場合: AOUTは"H"になり、M2 はオフになります。 $I_{LMAG}$ は負の値になるので、SWP (M1のドレイン)の電圧は $V_{IN}$ に向かって低下し、結果としてトランスの1次巻線電圧は小さくなります。トランスの動作により、2次巻線電圧も小さくなります。 $M_{CG}$ がオンの状態 (CSW が0V に保持された状態)で、トランスの2次巻線電圧が小さくなると、FSW は大幅に低下して0V に近づきます。

#### 領域6(図2)

共振リセットの場合と同様に、 $M_{FG}$ のボディ・ダイオードにより、FSWは最終的にはGNDよりダイオード1個分低い電圧にクランプされます。このボディ・ダイオードは、 $I_{LMAG}$ を2次巻線を通じて出力インダクタの方向に導通させます。 $M_{FG}$ のボディ・ダイオードと $M_{CG}$ はオンしているので、2次巻線電圧はダイオード1個分の電圧にクランプされます。トランスの動作により、SWPの電圧は $V_{IN}$ とほぼ同じ電圧にクランプされます。 $I_{LOUT}$  -  $I_{LMAG}$ は、 $I_{LOUT}$  -  $I_{LMAG}$ は、 $I_{LOUT}$  がトランスの2次巻線を通じて $I_{LOUT}$  がトランスの2次巻線を可能などからな2000では、 $I_{LOUT}$  がトランスの2次巻線を通じて $I_{LOUT}$  がトランスの2次巻線を可能などからな2000では、 $I_{LOUT}$  がトランスの2次巻線を2000では、 $I_{LOUT}$  がトランスの2の2の2の2000では、 $I_{LOUT}$  がトランスの2の2000では、 $I_{LOUT}$  がトランスの2の2000では、 $I_{LOUT}$

#### LT8311の同期制御方式

LT8311には、以下に示す2つの同期制御モードがあります。

- 1. **プリアクティブ・モード**:パルス・トランスは不要で、軽負荷 時にはDCM動作になります。PMODEピンを0Vに接続す ることによってイネーブルされます。MCGの両端にショット キ・ダイオードを使用します(図20)。

- 2. **同期モード**:パルス・トランスが必要で、軽負荷時には FCM動作またはDCM動作になります。PMODEピンを INTV<sub>CC</sub>に接続することによってイネーブルされます。

## プリアクティブ・モードの同期制御

#### プリアクティブ・モードでの Mcg のオン/オフのタイミング

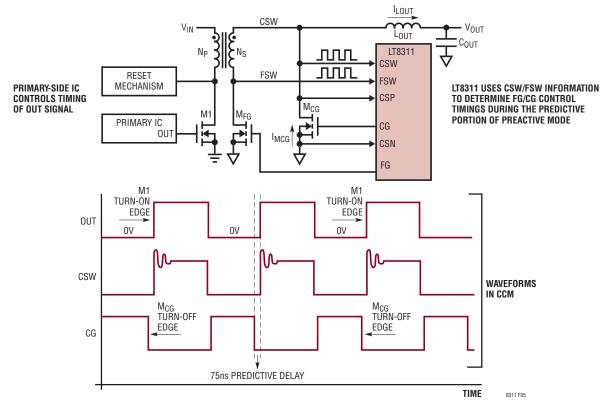

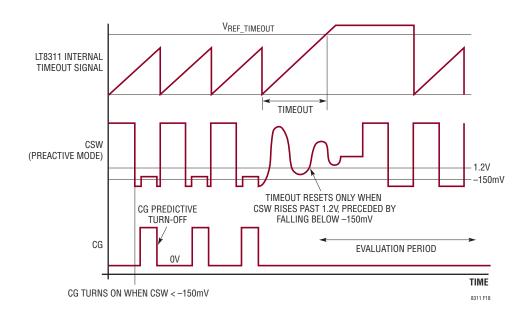

「プリアクティブ (preactive)」とは、「予測 (predictive)」と「反応 (reactive)」の短縮形です。プリアクティブ・モードでは、LT8311 は1次側ICと通信せずに2次側の同期 MOSFET を制御します。プリアクティブ・モードでは、キャッチ MOSFET ( $M_{CG}$ )がオンするのは(図5のCG立ち上がりエッジ)、キャッチ MOSFETのドレイン (CSW)の電圧が $_{-150mV}$ より低いことが検出され、さらにフォワード MOSFET ( $M_{FG}$ )がオフであることが検出されたときです。 $M_{CG}$ がオフするのは、 $M_{CG}$ がオンした後に上記2事象のどちらかが先に起こったときです。

- ・ MCG の予測型ターンオフ(図5): 予測型ターンオフでは、LT8311は、M1が次のサイクルでオンするタイミングを予測して、M1がオンする100ns前にMCGをオフします。MCGの予測型ターンオフにより、MCGとM1との相互導通が防止されます。M1がオンするタイミングを予測するには、現在と過去のCSWサイクルの立ち上がりエッジに位相を同期させます。予測型ターンオフは、M1のターンオン・エッジの周期性という固定周波数動作に固有の側面に依存します。さらに、予測型ターンオフはシステムのデューティ・サイクルに依存しないように設計されているので、負荷トランジェント/入力トランジェント時でもMCGを正確にオフすることができます。予測型ターンオフは通常、CCMでの中心的なMCGターンオフ機構になります。

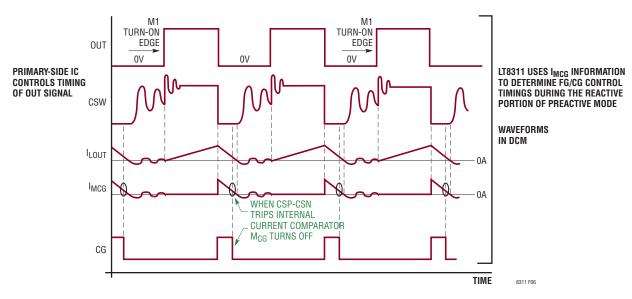

- MCGの反応型ターンオフ(図6):反応型ターンオフでは、フォワード・コンバータが軽負荷時にDCMでの動作を強制されます。反応型ターンオフでは、MCGを流れる電流(I<sub>MCG</sub>)によってLT8311内部の電流コンパレータが作動すると、LT8311がMCGをオフします。この電流コンパレータの入力はCSPピンとCSNピンです。通常、CSPピンと

CSNピンは、MCGを流れる電流がほぼ0になると作動するように構成されていますが、これは出力インダクタを流れる電流が0に近いことに対応します。反応型ターンオフは通常、DCMでの中心的なMCGターンオフ機構になります。

LT8311のプリアクティブ・モードでは、予測型部分と反応型部分の間を継ぎ目なく移行するので、キャッチMOSFETを適切な時間にオフして、相互導通や電子雪崩現象を回避することができます。

#### プリアクティブ・モードでの MFG のオン/オフ

プリアクティブ・モードでは、 $M_{FG}$ がオンするのは、 $M_{CG}$ のターンオフ・エッジが検出され、フォワードMOSFETのドレイン(FSW)の電圧が1.2Vより低いことが検出された後です。FSWの電圧が1.2Vより低くなるまで待つことにより、トランスのリセットがほぼ完了することが保証されます。 $M_{FG}$ がオフするのは、CSWの電圧が-150mVより低いことが検出されたときです。

プリアクティブ・モードで各MOSFETがオンする必要があるのは、他方のMOSFETのターンオフ・エッジが検出された後だけなので、このシステムには、2つのMOSFETの一方がスイッチングを開始する開始点が必要です。プリアクティブ・モードの開始点となるのは、 $M_{CG}$ を初めてオンしてスイッチングを開始した時点です。

#### プリアクティブ・モードでのシャットダウンと起動

同期制御の滑らかな起動と、この機構のシャットダウンを必要に応じて容易にするため、プリアクティブ・モードは多くの機能を盛り込んで設計されています。LT8311は、スイッチング動作を始める前にフォワード・コンバータの2次側の状態を評価して、スイッチングを開始できるかどうかを判定します。評価期間が終了するのは、連続3回のCSWスイッチング・サイクル期間(立ち上がりエッジ間)にわたって具体的な4つの条件を満たしたときです。いずれかの条件に反した場合、評価期間はリセットされ、スイッチング動作は停止状態となります。この評価期間中、2次側の電流はMCGとMFGのボディ・ダイオードを通って流れます。4つの条件は以下のとおりです。

- 1. VINの方がUVLO電圧よりも大きいこと

- 2. INTV<sub>CC</sub>はUVLO/OVLOの許容範囲内であること

- 3. TIMER ピンはタイムアウトしないこと。この機能が存在するのは、1次側がスイッチングを停止した場合にLT8311がスイッチングを停止するのを保証するためです。

図5. プリアクティブ・モードの予測動作の間、LT8311 は位相を CSW の 立ち上がりエッジに同期させ、このエッジの 75ns 前に McG をオフする

図 6. プリアクティブ・モードの反応動作の間、 $M_{CG}$  を流れる電流 ( $I_{MCG}$ ) によって LT8311 内部の電流コンパレータが作動すると、LT8311 は  $M_{CG}$  をオフする。コンパレータの入力は CSP と CSN なので、電流検出の作動電圧は、CSP/CSN に接続する直列抵抗を適切に選択することで設定される

LINEAR TECHNOLOGY

4. 「電流サンプル期間」と呼ばれる150nsの期間内に、CSP ピンとCSNピンが内部電流コンパレータを作動させないこと。この機能は、LT8311が同期式の導通を停止状態に保 つ時間内に非常に軽負荷の状態を検出し、それによってシステム効率を改善するのに役立ちます。

#### 電流サンプル期間が機能する仕組み:

電流サンプル期間は、所定のサイクル内にMCGがオンするかどうかにかかわらず存在します。CSWの電圧が-150mVより低いことが検出されると、LT8311は200nsの空白時間を開始します。この空白時間が完了すると、LT8311は150nsの電流サンプル期間を開始します。CSP/CSNピンの入力によってこの150nsの期間中に内部電流コンパレータが作動すると、LT8311は非常に軽負荷の状態とみなし、その時点で同期式の導通を停止してもう一度評価期間を開始します。「アプリケーション情報」セクションの「プリアクティブ・モードでの電流検出コンパレータのCSP/CSN入力の構成」を参照してください。

連続3回のCSWサイクルで4つの条件がすべて当てはまる場合、評価期間は終了し、LT8311はスイッチングの開始準備を行います。LT8311が最小オン時間の間MCGをオンすることでスイッチングが開始されます。スイッチング動作中の任意の時点で上記4条件のいずれかに反している場合、LT8311は同期式の導通をすべて停止し、評価期間を再開します。

プリアクティブ・モードの起動時に、LT8311はM<sub>CG</sub>のオン時間を内部でソフトスタートするので、フォワード・コンバータは、M<sub>CG</sub>の導通が全サイクル非同期の状態(2次側電流はM<sub>CG</sub>のボディ・ダイオードを通って流れる状態)からM<sub>CG</sub>の導通が全サイクル同期の状態に徐々に移行できます。

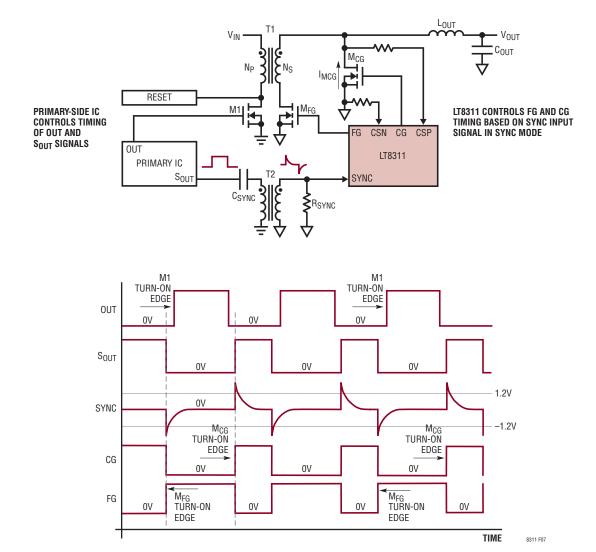

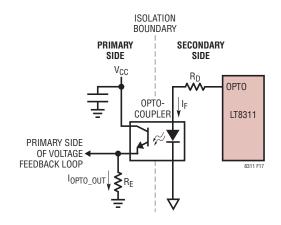

#### 同期モードの同期制御

同期モードでは、LT8311は軽負荷時に強制連続モード (FCM)で動作できます。同期モードでは、LT8311が1次側の ICから同期制御信号を受信するためにパルス・トランス(図7のT2参照)が必要です。キャッチMOSFETおよびフォワード MOSFETをオン/オフするため、これらの制御信号はLT8311によってデジタル式に("H"または"L"と)解釈されます。

FCM動作では、インダクタ電流を負にすることにより、フォワード・コンバータが軽負荷時に不連続導通モード(DCM)で動作しないようにすることができます。したがって、負荷がゼロの場合でもインダクタ電流は流れ続け、コンバータは固定周波数で動作します。

#### 同期モードでの McG のオン/オフのタイミング

同期モードでは、 $M_{CG}$ がオンするのはSYNCピンの信号が 1.2Vより高くなったときです。 $M_{CG}$ がオフするのはSYNCピン の信号が-1.2Vより低くなったときです。

#### 同期モードでの MFG のオン/オフのタイミング

同期モードでは、 $M_{FG}$ がオンするのはSYNCピンの信号が-1.2Vより低くなったときです。 $M_{FG}$ がオフするのはSYNCピンの信号が1.2Vより高くなったときです。

$R_{SYNC}$ と $C_{SYNC}$ による時定数を適切に選択して、特定のオーバードライブ電圧で十分なパルス幅を生成する必要があります(「アプリケーション情報」セクションの「パルス・トランスと高域通過フィルタの選択」を参照)。 $C_{SYNC}$ および $R_{SYNC}$ の標準値は、それぞれ 220pF および 560 $\Omega$ です。

#### 同期モードでのシャットダウン

同期モードでは、以下の条件のいずれかに合致する場合、LT8311は2次側のMOSFET  $(M_{CG}$  および $M_{FG})$ を両方ともオフにします。

- 1. VINの方がUVLO電圧よりも小さいこと

- 2. INTV<sub>CC</sub>はUVLO/OVLOの許容範囲外であること

- 3. TIMER ピンはタイムアウトしていること(TIMER ピンの抵抗のプログラミングに関する詳細については、「アプリケーション情報」セクションを参照)。

- 4. CSPピンとCSNピンは、MCGのオン時間中にLT8311の内部電流コンパレータを作動した。MCGを流れる電流(IMCG)は、400nsの空白時間経過後に検出されます。この空白時間はMCGのターンオン・エッジから始まります。同期モードでのCSPピンとCSNピンの構成に関する詳細については、「アプリケーション情報」セクションを参照してください。

図7. 同期モードでは、1次側のICがパルス・トランスを介してLT8311のSYNCピンに $S_{OUT}$ 信号を送信する。 SYNCピンの電圧が1.2Vより低いと $M_{FG}$ はオンになり、 $M_{CG}$ はオフになる。 SYNCピンの電圧が1.2Vより高いと $M_{CG}$ はオンになり、 $M_{FG}$ はオフになる。

LINEAR

#### オプトカプラの制御

LT8311は、オプトカプラを制御して、フォワード・コンバータ内で2次側から1次側に出力電圧を帰還させることができます。1次側のICと組み合わせて使用することにより、システム全体で、優れた入力/負荷レギュレーションおよび迅速なトランジェント応答特性を備えた固定周波数ピーク電流モード制御機能を実現します。

LT8311のオプトカプラ制御方式の基本を理解するには、図8を参照してください。LT8311は、FBピンに接続された抵抗分割器  $(R_{FB1}$  および $R_{FB2}$ )によって出力電圧を検出します。FBピンの電圧は、次の2つの入力のうち低い方の電圧と比較されます。

- 1.227Vの内部電圧リファレンス

- ソフトスタート(SS)ピンの電圧

起動時に、SSピンのコンデンサ(CSS)は、LT8311の10μA内部調整電流源によって充電されます。FBピンの電圧はSSピ

ンの電圧と1.227Vのリファレンスのうち低い方の電圧を追跡するので、FBピンの電圧(および拡大解釈すれば出力電圧)は、SSピンに接続されているコンデンサ(Css)によって設定されたスルーレートで強制的にソフトスタートが行われます。

注記:コンバータのソフトスタート時間をLT8311のSSコンデンサ(CSS)で確実に制御するため、1次側ICのソフトスタート時間を短く設定して、影響を受けないようにすることが重要です。この操作を行わないと、コンバータのソフトスタート時間の制御は1次側ICのソフトスタートが主体となり、LT8311は、1次側ICが設定した長いソフトスタート時間に合わせるためにSSピン電圧とスルーレートを調整するだけになります。

SSピンの電圧が 1.227V のリファレンスより高くなると、FBピンの電圧は 1.227V のリファレンスを追跡し始めます。したがって、出力は  $R_{FB1}/R_{FB2}$  の分割器回路網と FBピンのレギュレーション電圧である 1.227V によって設定された電圧に安定化されます。SSピンのコンデンサは、その内部クランプ電圧である 2V に達するまで、 $10\mu$ A の電流源によって充電され続けます。

図8. LT8311は、ピーク電流モード制御システムの一部として、フォワード・コンバータ内で電圧帰還を実現する

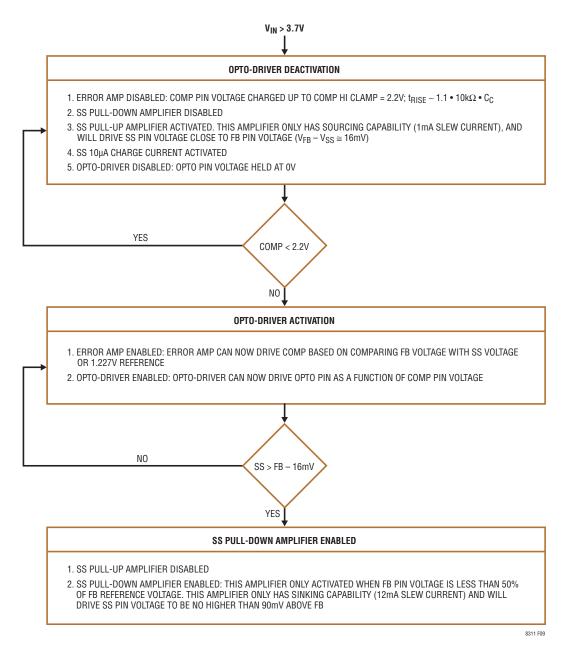

図9. 起動時のLT8311オプトカプラ制御動作のフローチャート

SSピンが2Vまで充電された状態で、FBピンの電圧と1.227Vのリファレンスの間に電圧差があると、トランスコンダクタンス・エラーアンプ(A1)はその出力(COMP)からシンク電流またはソース電流を供給します。COMPピンは、0.9Vのオフセットがありますが、オプトドライバ(A2)の入力として機能します。出力負荷電流の増加によってFBピンの電圧が1.227Vより低くなると、A1はCOMPピンを"H"に駆動します。COMPが"H"になると、A2はOPTOを強制的に"L"に駆動するので、RDを通ってオプトカプラに流れ込む電流量は低下します。

オプトカプラの出力電流はその入力電流に正比例するので、このオプトカプラの入力電流が減少すると、その出力電流、したがって $R_E$ でのエミッタ電圧も同様に減少します。 $R_E$ の電圧が低下すると、A3はその反転動作により、出力( $V_C$ )をより高い電圧に駆動します。 $V_C$ の電圧が高くなると、コンパレータ(A4)は抵抗 $R_{SNS}$ の両端の検出電圧を高くするよう制御し、より高いピーク電流で動作するようM1を制御します。M1を流れる電流は出力インダクタ電流(M1の電流・ $N_P/N_S = I_{LOUT}$ )に正比例するので、M1のピーク電流の増加は出力イ

83111

ンダクタのピーク電流の増加に変換されます。帰還ループが 制御しているのは、実質的には出力インダクタのピーク電流が 負荷電流増加の需要を満たすことであり、さらに最終的な目 標は出力電圧が負荷ステップから回復し、安定状態で推移す るのに役立つことです。

#### 起動時のオプトカプラ制御操作

LT8311のV<sub>IN</sub>ピンをコンバータの出力に直接接続するアプリ ケーションでは、LT8311は、オンしたときに1次側MOSFET のスイッチングに割り込みが生じないようにするインテリジェ ント回路を組み込んでいます。LT8311は、そのVINピンの電圧 (したがって V<sub>IN</sub>を出力に直接接続した場合のコンバータの 出力電圧)が3.7Vを超えるとオンします。インテリジェント回 路がない場合は、このVOUTのレベルによってLT8311のFB ピンの電圧がLT8311のSSピンの電圧(ICがオンすると標準 で0V)より高くなるので、アンプA1はCOMPピンを"L"に駆 動します。これによりOPTOピンは"H"になるので、全電流が オプトカプラに流れ込み、1次側MOSFETのスイッチングは終 了します。1次側MOSFETのスイッチングが終了すると、コン バータの出力電圧低下につながることがあるので、LT8311が 電源を失って停止する可能性があります。LT8311のインテリ ジェント回路は、2つの独自機能を使用してこの状況を防止し ます。このデバイスには、V<sub>IN</sub>のUVLO電圧に100mVのヒス テリシスが組み込まれているので、電源が投入された時点で、 再び電源を失うまでは $V_{IN}$ ピンの電圧が最大100mV低下し ても耐えることができます。さらに重要なのは、LT8311 はその 「オプトカプラ制御の中枢部」をオフ状態に維持するオプトカ

プラ制御の起動システムを備えていることです。オフ状態に維持される期間は、電圧ループが最終的にイネーブル状態になると、電圧ループ内にあるすべての関連ノード電圧がスイッチング動作を停止しない状態まで、これらのノード電圧にバイアスが事前に印加されるまでです。

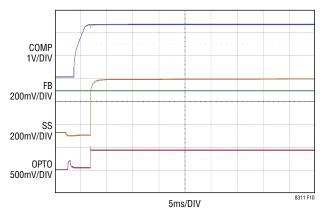

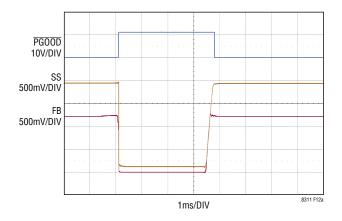

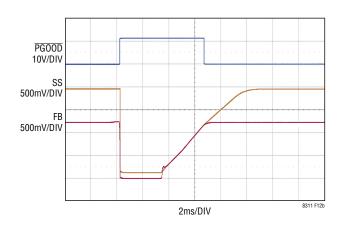

図9および図10のオシロスコープ写真に示すように、LT8311の起動時のオプトカプラ制御動作には、SSピンの電圧をFBピンの電圧近くまで急上昇させ、COMPピンの電圧を高い方のクランプ電圧まで急上昇させて、OPTOピンの電圧を"L"に維持することを伴います。この段階では、インダクタ電流(および拡大解釈すれば出力電圧)は、1次側ICが備えているソフトスタート機能によって制御されます。状態マシンが完成すると、LT8311は帰還ループを再び動作可能な状態にできるので、FBピンの電圧は、最終的にそのレギュレーション目標値である1.227Vに到達するまでLT8311のSSピンの電圧を追跡します。

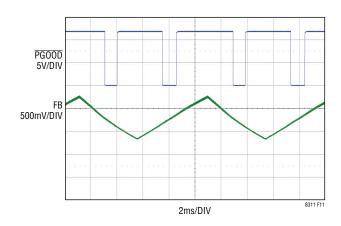

#### パワーグッド

LT8311は、システム・レベルの設計を支援する出力パワーグッド・モニタリング機能を備えています。FBピンの電圧が175µsの期間1.227Vリファレンスの±7%の範囲内にとどまると、LT8311のPGOODピンは内部で"L"になります。175µs経過するのを待つと、トランジェントの発生時にPGOODピンが誤検出を示さないようになります。PGOODコンパレータには±3%のヒステリシスがあります。したがって、FBピンの電圧を1.227Vの安定値から±10%遠ざけると、PGOODピンの内部

図10. 起動時のオプトカプラ制御動作

図11. パワーグッドが作動する(PGOOD = "L")のは、LT8311のFBピンの電圧がその安定化目標値(1.227V)の±7%以内にある場合である。PGOODピンの電圧は、100kの外付け抵抗を介して12Vのハウスキーピング電源まで外部から引き上げられる

83111

23

プルダウン回路によって直ちに停止します。その結果、このピンは、外付け抵抗または外部電流源を電源電圧に接続することにより"H"になります。PGOODピンの出力は、出力電圧の状態に応じて判断するマイクロコントローラに供給できます。

#### 出力オーバーシュート制御による短絡回復の支援

FBピンの電圧がFBリファレンス電圧(1.227V)の50%未満である限り、LT8311は、そのソフトスタート・プルダウン・アンプ(「ブロック図」のSSDOWNAMP)を起動することにより、出力オーバーシュート制御を実現します。これは、短絡状態や重負荷トランジェントを解消した後の出力電圧回復時に特に役立ちます。SSプルダウン・アンプは、SSピンの電圧がFBピンの電圧より100mV以上高くならないように、必要な量の電流

を(その最大シンク能力である13mAまで)吸い込みます。出力短絡時に、FBピンの電圧がグランドまで低下すると、SSプルダウン・アンプが起動し、SSピンの電圧はFBピンの電圧より100mV高くなります。最終的に短絡状態が終わると、FBピンの電圧は、CSSと10µAの充電電流によって設定されたスルーレートで、SSピンの電圧とともに徐々に上昇します。これにより、出力は短絡状態から徐々に回復することができます。フォワード・コンバータの出力からLT8311のVINピンに直接電力を供給すると、短絡時にはその制御中枢部をすべて失うことに注意してください。このシナリオでは、LT8311が制御中枢部を取り戻すまで出力オーバーシュート制御は無効になります。その時点に達するまで、出力インダクタ電流と出力電圧は1次側ICのソフトスタート機能によって制御されます。

(a)  $C_{SS} = 1$ nFの場合の出力オーバーシュート制御。LT8311の $V_{IN}$ の電力を12Vのハウスキーピング電源から供給。これを使用して、100kの外付け抵抗を介して $\overline{PG00D}$ ピンもプルアップ

(b)  $C_{SS} = 33$ nF の場合の出力オーバーシュート制御。 LT8311の $V_{IN}$  の電力を12V のハウスキーピング電源から供給。 これを使用して、100k の外付け抵抗を介して $\overline{PG00D}$  ピンも プルアップ

図12. 起動時の出力オーバーシュート制御

#### VINのバイアス電源

LT8311の $V_{IN}$ ピンにはさまざまな方法で電力を供給できます。 このピンの近くには $2.2\mu$ F以上のセラミック・コンデンサを配置してください。

LT8311に電力を供給する適切なバイアス電源を選択するには、以下の基準を検討することが必要です。

- 1.  $V_{IN}$ ピンは、ある一定の構成では、キャッチMOSFETとフォワードMOSFETにゲート駆動電圧を供給するLT8311の INTV<sub>CC</sub>ピンへの唯一の電源にすることができます。そのような状況では、 $V_{IN}$ のバイアス電源電圧を十分高くして、両方の同期MOSFETに適度なゲート駆動電圧(標準で  $5V \sim 7V$ )を供給できるようにする必要があります。

- 2. V<sub>IN</sub>のバイアス電源は、以下の電流を供給できる必要があります。

- a. LT8311のV<sub>IN</sub>電流(標準4.5mA)

- b. V<sub>IN</sub>を使用してINTV<sub>CC</sub>ピンに電力を供給する場合のINTV<sub>CC</sub>ゲート駆動電流(標準で10mA ~ 30mA)

- c. オプトドライバのソース電流(標準で1mA~5mA)

- 3. VINの起動条件と短絡条件は以下のとおりです。

- a. LT8311が同期制御とオプトカプラ制御を開始するには、V<sub>IN</sub>が適度な時間内に起動する必要があります。同期制御が停止している間、2次側の電流は2次側の同期 MOSFETのボディ・ダイオードを流れます。1次側のLT3752、LT3752-1、またはLT3753と連動させる場合は、オプトカプラ制御がオフになっている間、フォワード・コンバータは開ループで動作し、ボルト秒クランプを使用してV<sub>OUT</sub>を制御します。

- b. トランジェント時にはV<sub>IN</sub>がGNDに短絡する場合があります。たとえば、出力電圧から電力が供給されるV<sub>IN</sub>は、出力短絡時に0Vになります。フォワード・コンバータはLT8311の電源の瞬間的な喪失を乗り切ることができる必要がありますが、これは多くの場合、1次側ICのソフトスタート制御を適切に設定すれば容易に達成されます。1次側ICのソフトスタート制御の設定の詳細については、LT3752/LT8310のデータシートを参照してください。

前述の基準を念頭に置くと、LT8311に電力を供給するには、以下に示す3つの方法 $(1\sim3)$ があります。プリアクティブ・モードでは、方法1、2、または3を使用します。同期モードのFCMでは、方法1または3を使用します。DCMでは、方法1、2、または3を使用します。

- 1. LT3752のハウスキーピング電源から電力を供給する(「標準的応用例」セクションの図21参照)。LT3752のハウスキーピング電源は、LDOではなくフライバック・コンバータとして、効率的な供給源です。この電源は外部巻線を介してLT8311のV<sub>IN</sub>ピンとINTV<sub>CC</sub>ピンに接続できます。キャッチMOSFETとフォワードMOSFETに適切なゲート駆動電圧を供給するには十分に高い電圧でありながら、効率損失と熱損失を最小限に抑えるのに十分な低電圧に設定できます。ハウスキーピング電源はLT3752が入力電力を受電するとすぐに起動するので、電力はLT8311に遅延なく伝達されます。

- 2. V<sub>OUT</sub>から直接電力を供給する。10V未満の出力電圧では、出力電圧の起動時間を慎重に検討し、出力電圧がレギュレーション状態に達する前にLT8311が起動して、同期制御/オプトカプラ制御を実現できるようにする必要があります。また、このように出力電圧が低いときは、外付けのMOSFETに十分なゲート駆動電圧を確実に供給できることも重要です。V<sub>OUT</sub>の電圧が高いときは、ICの内部電力損失に関連した効率と熱に関する検討事項が重要な基準になる可能性があります。さらに、V<sub>OUT</sub>の電圧が高いときは、V<sub>IN</sub>ピンに加わる電圧トランジェントがこのピンの絶対最大定格30Vを超過しないようにすることが重要です。

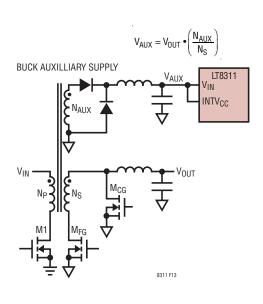

- 3. 図13に示すように、トランスの補助巻線による降圧回路を 使用する。この回路には効率が高いという利点があり、設 計するのがきわめて簡単です。このことは、外部ハウスキー ピング電源がない低出力電圧アプリケーション(3.3Vまた は5V)、および出力電圧から直接電力を供給することが不 適当なアプリケーションで特に役立ちます。この構成では、 2次側のスイッチング・パルスから降圧回路の出力電圧の エネルギーを引き出しており、このパルスはフォワード・コ ンバータの主要出力電圧(VOUT)のエネルギーも供給して います。降圧コンバータの出力電圧が時間内に十分上昇 し、フォワード・コンバータの実際の出力電圧がレギュレー ション状態に近づく前にLT8311を起動して同期制御とオ プトカプラ制御を実現するには、慎重な検討が必要です。 降圧コンバータの出力電圧が目標値に到達する時間を、 フォワード・コンバータの主要出力電圧の場合と比較して 短くする必要がある場合、簡単な方法は、たいていの場合

8311

は1次側ICのソフトスタート・コンデンサを大きくすることにより、主要出力電圧の起動時間を長くすることです。

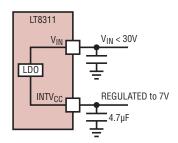

#### INTVccのバイアス電源

INTV<sub>CC</sub>ピンは、LT8311のキャッチ MOSFET およびフォワード MOSFET のゲート・ドライバに電力を供給します。図 14に示すように、INTV<sub>CC</sub>ピンにバイアスを与える構成は2つ存在します。

1. 最初の構成では、LT8311のオンチップLDOは、 $V_{IN}$ を電源としてINTV $_{CC}$ ピンの電圧を安定化します。 $V_{IN}$ ピンの電圧が低いと、内部LDOはドロップアウト状態で動作し、INTV $_{CC}$ ピンの電圧は $V_{IN}$ ピンの電圧より約 400mV低い電圧になります。 $V_{IN}$ ピンの電圧が高い場合、内部LDOはINTV $_{CC}$ の電圧を $T_{CC}$ で変定化します。 $T_{CC}$ の電圧を $T_{CC}$ で変定化します。 $T_{CC}$ の電圧がそのUVLO電圧(立ち上がりは $T_{CC}$ の電圧がそのUVLO電圧(立ち上がりは $T_{CC}$ の電圧がそのUVLO電圧(立ち上がりは $T_{CC}$ の電圧がそのUVLO電圧(立ち上がりは $T_{CC}$ のはい。INTV $T_{CC}$ の電圧がそのUVLO電圧(立ち上がりは $T_{CC}$ の間期スイッチングが停止します。INTV $T_{CC}$ のLDOが供給できる最大保証電流は $T_{CC}$ の2次側MOSFET( $T_{CC}$ のよびMFG)が必要とする全ゲート電荷( $T_{CC}$ )電流は $T_{CC}$ の名と確認してください。

$I_{MOSFET\_TOTAL} = f_{SW} \cdot (Q_{g\_MCG} + Q_{g\_MFG}) < 40 \text{mA}$

ここで、 $f_{SW}$ はコンバータのスイッチング周波数、 $Q_{g\_MCG}$ は $M_{CG}$ のゲート電荷( $Q_g$ )定格、 $Q_{g\_MFG}$ は $M_{FG}$ のゲート電荷( $Q_g$ )定格です。

この構成は、LT8311の内部LDOを利用しますが、ほとんどのアプリケーションに対して十分なものであり、制限される要因はLDOの電力損失に関連した熱的な検討事項だけです。電力損失を最小限に抑えると、LT8311の動作接合部温度を低くするのに役立つので、システムが動作する周囲温度範囲が広がる可能性があります。

LDOの電力損失 = (VIN - INTVCC) • IMOSFET\_TOTAL

LT8311の動作接合部温度 ≈

θJA • (V<sub>IN</sub> • 4.5mA + LDO の電力損失 + V<sub>IN</sub> • I<sub>OPTO</sub>) + T<sub>A</sub>

ここで $\theta_{JA}$ はLT8311の接合部-周囲雰囲気間熱抵抗であり、標準では38°C/Wです。 $I_{OPTO}$ はLT8311のOPTOピンによってオプトカプラに供給される電流です。4.5mAはLT8311の標準的な $V_{IN}$ 電流です。 $T_A$ は周囲温度です。

図13. 降圧回路がV<sub>AUX</sub>電源を生成、これにより、 LT8311のV<sub>IN</sub>ピンとINTV<sub>CC</sub>ピンに電力を供給

図14. VINとINTVCCのピン配置

LINEAR

2. 2番目の構成では、 $V_{IN}$ ピンのバイアス電源を $INTV_{CC}$ ピン に直接接続して駆動し、内部LDOを迂回しています。この 構成では、 $INTV_{CC}$  LDOの内部での電力損失が必要ないことにより、IC 内部での電力損失が減少します。 $V_{IN}$  の電圧が16V より低い場合は、CO このオプション構成を使用して  $INTV_{CC}$  に十分な余裕を与え、CO のC (+) 側電圧である C 16.5V 未満を維持できるようにします。C トランジェント発生 時にC 1V が C C の絶対最大定格電圧である C C C を超えないことを確認してください。

外部電源または補助巻線を使用できる場合は、この構成  $(V_{IN} \ge INTV_{CC} \ge E$  いに接続)を使用してICに電力を供給します。LT3752を1次側ICとして使用する場合は、この構成が最も適切です。「標準的応用例」セクションの図21に示すように、LT3752のハウスキーピング電源は補助巻線を介してLT8311の $V_{IN} \ge INTV_{CC}$ に接続できます。

INTV<sub>CC</sub>は、3種類の構成すべてについて4.7μF以上のセラミック・コンデンサを使用してグランドにバイパスしてください。 INTV<sub>CC</sub>ピンの近くにコンデンサを配置して、コンデンサのグランド端子がLT8311のグランド(露出パッド)までのできるだけ短い復帰経路になるようにしてください。

#### LT8311のオプトカプラ制御の基本

#### 出力電圧の設定

図15は、抵抗分割器帰還回路網によってフォワード・コンバータの出力電圧を設定する方法を示しています。R<sub>FB1</sub>の上端をVoutに、R<sub>FB1</sub>/R<sub>FB2</sub>のタップ点をFBピンに、R<sub>FB2</sub>の下端をグランドに接続します。R<sub>FB2</sub>のグランド帰路はLT8311のグランドにできるだけ近づける必要があり、かつフォワード・コンバータの電力経路から遠ざける必要があります。電力経路にはスイッチング電流が流れており、(負荷によっては)値の大きな電流が流れるので、意図しないノイズが発生することや、FBの抵抗分割器経路にI・R電圧降下が生じることがあります。FBピンは1.227Vに安定化されます。また、このピンから流れ出す標準の入力ピン・バイアス電流は120nAです。出力電圧は次式によって設定されます。

$$V_{OUT} = 1.227 \cdot \left(1 + \frac{R_{FB1}}{R_{FB2}}\right) - 120 \text{nA} \cdot R_{FB1}$$

図15. フォワード・コンバータの出力電圧の設定

83111

図 16. LT8311 が 2 次側にあり LT3752 (または) LT8310 が 1 次側にあるフォワード・コンバータの電圧帰還ループ

#### ループ補償部品の選択

図16はフォワード・コンバータに関連した標準的なループを示しており、2次側にLT8311を使用し、1次側ICとしてLT3752またはLT8310を使用しています。LT3752に固有のパラメータ値を赤で示し、LT8310に固有のパラメータ値を青で示します。ここに示すフォワード・コンバータのループは、ピーク電流モード制御システムです。

ループ補償の最適値は、1次側に使用するICとLT8311のほかに、コンバータの動作状態(入力電圧範囲、出力電圧、負荷電流など)によって変わります。LT8311周辺の電圧帰還ループを補償するには、通常はLT8311のCOMPピンとGNDの間に直列の抵抗/コンデンサ回路網を接続します。ほとんどのアプリケーションでは、コンデンサ $C_C$ の範囲は4.7nF~47nF、抵抗 $R_C$ の範囲は2k~20kにします。 $R_C$ の値が大きすぎると、デバイスは高周波ノイズとジッタの影響を受けやすくなります。 $R_C$ の値が小さすぎると、トランジェント性能が悪化します。 $C_C$ の値の選び方は、どちらかというと $R_C$ の選び方

の逆です。使用するCcの値が小さすぎるとループが不安定 になる可能性があり、使用するCcの値が大きすぎるとトラン ジェント性能が悪化する可能性があります。多くの場合は、 小容量のコンデンサ(CF)をRC補償回路網に並列に接続し て、出力電圧リップルから(内部エラーアンプを介して)生じる COMPピンの電圧リップルを減衰させます。コンデンサCFの 値の範囲は、通常10pF~100pFです。特定のアプリケーショ ンでは、位相進みが0のコンデンサCplを(抵抗RFR1と並列 ンに接続すると、ループのトランジェント性能を改善するの に役立つ場合があります。補償回路網を設計する実際的な 手法としては、このデータシートの回路の中から目的のアプリ ケーションに似た回路を選んで出発点とし、補償回路網を調 整して性能を最適化します。その後、負荷電流、入力電圧範 囲、温度などすべての動作条件にわたって安定性をチェック します。

LINEAR TECHNOLOGY

#### オプトカプラの選択

前に説明した電圧帰還ループは、オプトカプラを使用して出力電圧情報を2次側から1次側に伝達します(図17参照)。オプトカプラが使用される理由は、広く普及していて、比較的低コストであり、電位差が最大5000Vの絶縁境界を越えてDC信号情報を伝達できる能力を備えているからです。

オプトカプラの入力は通常は赤外発光ダイオード(LED)で構成されますが、出力はフォトトランジスタが標準です。オプトカプラの入力LEDに流れ込む電流(I<sub>F</sub>)によって、光子が放出されます。これらの光子はオプトカプラの絶縁障壁を越えて、出力フォトトランジスタのベースに集まります。この光電流は、実質的にフォトトランジスタのベース電流を発生しますが、オプトカプラから流れ出る前にフォトトランジスタのB(電流利得)によって増加し、IOPTO\_OUTと呼ばれます。オプトカプラの注目の主要パラメータは電流伝達率(CTR)です。CTRは通常は%単位で表現され、以下のように計算されます。

$$CTR(\%) = \frac{I_{OPTO\_OUT}}{I_F}$$

ここで、 $I_{OPTO\_OUT}$ はオプトカプラの出力電流で、 $I_F$ はオプトカプラの入力LED電流です。

オプトカプラは歴史的に毛嫌いされてきましたが、それも当然で、CTRが動作時間の経過とともに低下し、また動作温度が高くても、入力電流  $(I_F)$  が高くても CTRが低下するからです。この CTR 低下の多くは、入力 LED の量子効率の低下が原因であり、量子効率は LED の動作電流  $(I_F)$ 、動作温度、および動作期間の関数です。

幸いにも、LED技術はここ数十年間に成熟し、オプトカプラの性能が改良できるようになりましたが、その解説はこのデータシートの範囲外です。Avago Technologies 社は、AlGaAs タイプのLEDで製造され、デューティ・サイクル100%、周囲温度85°C、入力電流  $(I_F)$ 5mAで動作するオプトカプラが現場で30年を超えて動作しても、CTR低下の3 $\sigma$ がわずか10%にすぎないことを示す文書を発表しました。

オプトカプラの詳細については、Avago Technologies、CEL、 Vishay などのオプトカプラ・メーカーのアプリケーションノート やデザインノートを参照してください。標準的な推奨オプトカプ ラは、California Eastern Laboratories (CEL)製の PS2801です。

図17. 電圧帰還ループでの標準的なオプトカプラ構成

#### オプトカプラの設計ガイダンス

オプトカプラのCTR低下は、以下の2つの点でフォワード・コンバータの電圧帰還ループに影響します。

- 1. 大信号の影響:CTRの低下は、オプトカプラから同じ出力電流を維持するために、オプトカプラの入力電流を増加する必要があることを意味します。オプトカプラの入力電流はLT8311のOPTOピンから供給されます。光帰還ループは、考えられる最低のCTRでLT8311のOPTOピンの電流が制限されないように設計します。LT8311の内部オプトドライバがOPTOピンから供給できる最大電流は10mAです。OPTOピンがオプトカプラの入力に供給する最大電流が公称で2mA~3mAになるように、システムを設計します。

- 2. 小信号の影響: CTR が 1/2 に低下した場合、それ以外のすべてのパラメータが一定であると仮定すると、フォワード・コンバータの電圧帰還ループのDC 利得およびクロスオーバー周波数は 1/2 に低下します。同様に、CTR が 2 倍に増加した場合、他のパラメータが変化しないと仮定すると、電圧帰還ループのDC 利得およびクロスオーバー周波数は 2 倍に増加します。電圧帰還ループは、CTR<sub>(MAX)</sub> (オプトカプラの CTR が最大)のとき、帰還ループのクロスオーバー周波数がシステムのナイキスト周波数(=スイッチング周波数/2)の範囲内に十分にとどまるように設計する必要があります。経験上の目安としては、電圧帰還ループのクロスオーバー周波数を、CTR の公称値でのオプトカプラのスイッチング周波数の約 1/10で設計します。

前に説明したように、オプトカプラ技術における改良により、オプトカプラの全動作期間でのCTRの変化はきわめて小さくなり、十分に制御されるようになりました。しかしながら、オプトカプラの設計でより難易度の高い側面は、大きなサンプル・サイズと広い動作温度範囲でのCTRの絶対的な変化です。オプトカプラ・ベースの電圧帰還ループを設計する場合、考慮が必要なのはCTRのこの広がりです。CTRの変化が公称値の2倍以内であるオプトカプラを選べば、通常は妥当な出発点になります(室温でのCTRの広がりが小さいオプトカプラの一覧については表1を参照してください)。

次のガイドラインは、一般的なアプリケーションでオプトカプラの入力抵抗と出力抵抗(それぞれ $R_D$ および $R_E$ )の初期値を計算するのに役立ちます。 $R_D$ と $R_E$ の最終値は、システムのブレッドボード作成後に決定します。以下のガイドラインを読む場合は、参照先として図 16を使用してください。

**ステップ1**:1次側ICのエラーアンプの反転利得 $\Omega$ を設定する抵抗(R1およびR2)を選択します。R1の標準的な初期値は、LT3752では22kであり、LT8310では100kです。R2の標準的な初期値は、LT3752では33kであり、LT8310では150kです。

**ステップ2:**1次側ICのCOMPピンまたは $V_C$ ピンを、インダクタ電流をゼロにするのに必要な電圧(次の式の $V_{CLOW}$ のこと)まで駆動するために、オプトカプラの出力トランジスタ( $V_{X\_MAX}$ )のエミッタで必要な最大電圧を計算します。

$$V_{X\_MAX} = V_{REF} \left[ 1 + \frac{R1}{R2} \right] - V_{C\_LOW} \bullet \frac{R1}{R2}$$

$V_{C\_LOW}$  は LT8310 では 0.7V で、 LT3752 では 1.25V です  $V_{REF}$  は LT8310 では 1.6V で、 LT3752 では 1.25V です。

**ステップ3**: オプトカプラ出力電流の最大値( $I_{OPTO\_OUT\_HIGH}$ ) を  $1mA \sim 10mA$  の範囲から選択します。 $I_{OPTO\_OUT\_HIGH}$ の標準的な選択値は、たとえば 2.5mA です。ここで、 $R_E$  を次のように計算します。

$$R_{E} = \frac{V_{X-MAX}}{I_{OPTO\_OUT\_HIGH}}$$

**ステップ4**: LT8311のOPTOピンによってオプトカプラに供給する必要がある最大入力電流( $I_{F,HIGH}$ )を、オプトカプラのCTRが最小の場合(CTR $_{MIN}$ )について概算します。

$$I_{F\_HIGH} = \frac{I_{OPTO\_OUT\_HIGH}}{CTR_{MIN}}$$

LT8311のOPTOピンが供給できる10mAの制限範囲内に IF HIGHが十分入っていることを確認してください。

**ステップ5**: OPTOピンの電圧が最大( $V_{OPTO(MAX)}$ )のとき、OPTOピンが電流  $I_{F\_HIGH}$ を供給するために必要な $R_D$ の値を概算します。オプトカプラの入力 LED のオン電圧は 1.2V です。

$$R_D = \frac{V_{OPTO(MAX)} - 1.2V - 0.5V}{I_{F HIGH}}$$

LINEAR

この式で0.5Vをさらに減算しているのは、OPTOピンの線形特性範囲を考慮し余裕を持たせたものです。LT8311の $V_{IN}$ ピンの電圧が8V以上の場合、OPTOピンの最大電圧は6V(保証される最小の値)です。 $V_{IN}$ ピンの電圧がそれより低い場合、 $V_{OPTO\ MAX}$ は $V_{IN}$  - 1.7Vになります。

前の式は、オプトカプラ・ベースの電圧帰還ループの大信号特性に対して $R_D$ および $R_E$ をどのように計算する必要があるかを示しています。 $R_D$ および $R_E$ に対して最終的に選ばれた値は、電圧帰還ループの大信号特性と小信号特性の両方にうまく折り合いをつけるために、ここで計算した値から調整することが必要な場合があります。

# 出力ソフトスタートのためのソフトスタート・コンデンサ (Css)の選択

「動作」セクションでは、起動時の出力ソフトスタート、短絡回復時の出力オーバーシュート制御、さらにLT8311のオプトカプラ制御方式の起動時での電圧帰還ループに対するバイアスの事前印加に対して、LT8311のSSピンがどのように役立つかについて説明しました。ソフトスタート・コンデンサ(Css)は、起動時にLT8311の10µA内部調整電流源によって充電されます。SSピンの電圧が1.227Vより低いとFBピンの電圧はSSピンの電圧を追跡するので、SSピンのスルーレートを設定するとFBピンのスルーレートも設定され、出力電圧がそのレギュレーション電圧に到達する時間が設定されます。「動作」セクションで説明したように、SSピンのスルーレートとFBピンのスルーレートの間のトラッキングが有効なのは、LT8311の出力電圧のソフトスタートが1次側ICの出力電圧のソフトスタートより低速である場合に限ることを認識することが重要です。この基準に従うことにより、次式が適用されます。

$$\frac{\partial V_{OUT}}{\partial t} = \frac{\partial V_{FB}}{\partial t} = \frac{10 \mu A}{C_{SS}}$$

ここで、 $C_{SS}$ はLT8311のSSピンとGNDの間のコンデンサ、 $V_{OUT}$ はフォワード・コンバータの出力電圧、 $V_{FB}$ はLT8311のFBピンの電圧です。

定常状態では、SSピンの電圧は内部クランプによって最大 2V にクランプされます。

#### LT8311の同期制御の基本

#### キャッチ MOSFET およびフォワード MOSFET の選択

2次側の同期MOSFETを選択するときは、パラメータ(ドレイン-ソース間の最大電圧、ドレイン-ソース間の最大電流、ゲート-ソース間の最大電圧)を慎重に選択して、システムの堅牢な動作を確保することが重要です。さらに、システム効率を最大限に高めるため、MOSFETのオン抵抗( $R_{DS(ON)}$ )およびゲート電荷( $Q_g$ )を最小限に抑えて、MOSFETでの電力損失を少なくすることが重要です。特定のアプリケーションに対して適切なキャッチMOSFETおよびフォワードMOSFETを選択するには、以下のガイドラインに従ってください。

#### 1.Vpsの最大定格

キャッチ MOSFET のドレインで観測される最大電圧は、システムの最大入力電圧  $(V_{IN(MAX)})$  とトランスの巻数比  $(N_S/N_P)$  の関数です。

Catch MOSFET

$$V_{DS(MAX)} = V_{IN(MAX)} \cdot \frac{N_S}{N_P} \cdot Margin$$

ここで、Margin (余裕)は1から3まで(標準では1.5~2)の数で、キャッチMOSFETのV<sub>DS(MAX)</sub>の式に一定の安全余裕を与えます。これは、トランスの2次巻線の漏れインダクタンスに付随した電圧スパイクを考慮したものです。キャッチMOSFETのドレインにスナバ回路を使用すると、漏れインダクタンスによるスパイクが最小限に抑えられ、Marginをその範囲の下端に近づけることができます。

フォワードMOSFETのドレインで観測される最大電圧は、トランスの磁束をリセットするためにフォワード・コンバータの1次側で使用されるリセット機構の関数です。

アクティブ・クランプ・リセットを使用する場合は、次のようになります。

Forward MOSFET

$$V_{DS(MAX)} \approx \frac{V_{OUT}}{1 - \frac{V_{OUT}}{V_{IN(MIN)} \bullet \frac{N_S}{N_P}}}$$

ここで、V<sub>IN(MIN)</sub>はシステムの最小入力電圧であり、V<sub>OUT</sub>はフォワード・コンバータの出力電圧です。フォワード MOSFET のV<sub>DS(MAX)</sub>に関するこの式では、1次側のアクティブ・クランプ・コンデンサ(C<sub>CL</sub>)が、電圧源として扱われるほど十分に大きいと仮定していることに注意してください。実際には、フォワード MOSFET のドレイン電圧には、ここで計算した電圧以上の「湾曲」があり、リセット処理時にL<sub>MAG</sub>とC<sub>CL</sub>の間を往復するエネルギーと関連しています。ほとんどのアプリケーションでは、フォワード MOSFET のV<sub>DS(MAX)</sub>の式に20%の安全余裕を加えることでこの湾曲を説明できます。

共振リセットを使用する場合は、次のようになります。

Forward MOSFET

$$V_{DS(MAX)} \approx \frac{V_{OUT}}{f_{SW} \cdot 2 \cdot \sqrt{L_{MAG} \cdot C_{RST}}}$$

ここで、f<sub>SW</sub>はフォワード・コンバータのスイッチング周波数、 L<sub>MAG</sub>はトランスの1次巻線の磁化インダクタンス、C<sub>RST</sub>は1 次側で使用される共振リセット・コンデンサです。

キャッチMOSFETとは異なり、フォワードMOSFETのVDS(MAX)の式は、通常は漏れインダクタンスによる電圧スパイクを考慮する必要はありません。これは、フォワードMOSFETのオン/オフが、蓄積された大量の漏れインダクタンス・エネルギーを消費しなければならないフォワードMOSFETのドレインとは通常は関係ないからです。

#### 2. Ips の最大定格

ほとんどのパワーMOSFETのデータシートでは、連続ドレイン電流およびパルスドレイン電流に定格があります。連続ドレイン電流はキャッチMOSFETおよびフォワードMOSFETのRMSドレイン電流で、これはインダクタ電流と、フォワード・コンバータが動作しているデューティ・サイクルの関数です。パルスドレイン電流はMOSFETで観測される瞬間的な最大ドレイン電流で、通常はインダクタ電流波形のピークです。

最大連続ドレイン電流を計算する前に、フォワード・コンバータの最小デューティ・サイクル、最大デューティ・サイクル、および平均デューティ・サイクルを計算すると役立ちます。

$$D_{MIN} = \frac{V_{OUT}}{V_{IN(MAX)} \cdot \left(\frac{N_S}{N_P}\right)}$$

$$D_{MAX} = \frac{V_{OUT}}{V_{IN(MIN)} \cdot \left(\frac{N_S}{N_P}\right)}$$

$$D_{AVG} = \frac{D_{MAX} + D_{MIN}}{2}$$

ここで、 $V_{IN(MAX)}$ と $V_{IN(MIN)}$ は、フォワード・コンバータの最大入力電圧と最小入力電圧です。

キャッチMOSFETの最大連続ドレイン電流 ( $I_{CAT\_RMS}$ ) は、次のように計算できます。

$$I_{CAT\_RMS} = \sqrt{(1 - D_{MIN}) \cdot \left(I_{LOAD(MAX)}^{2} + \frac{I_{RIPP(P-P)}^{2}}{12}\right)}$$

ここで、D<sub>MIN</sub>はフォワード・コンバータの最小デューティ・サイクル、I<sub>LOAD(MAX)</sub>はフォワード・コンバータの最大出力負荷電流、I<sub>RIPP(P-P)</sub>は出力インダクタを流れるピーク・トゥ・ピークのリップル電流です。I<sub>RIPP(P-P)</sub>は次のように計算されます。

$$I_{RIPP(P-P)} = V_{OUT} \bullet \frac{1 - D_{AVG}}{f_{SW} \bullet L_{OUT}}$$

ここで、DAVG はフォワード・コンバータの平均デューティ・サイクル、f<sub>SW</sub> はコンバータのスイッチング周波数、L<sub>OUT</sub> は出力インダクタンスの値です。

フォワードMOSFETの最大連続ドレイン電流(I<sub>FWD\_RMS</sub>)は次のとおりです。

$$I_{FWD\_RMS} = \sqrt{D_{MAX} \cdot \left(I_{LOAD(MAX)}^{2} + \frac{I_{RIPP(P-P)}^{2}}{12}\right)}$$

フォワードMOSFETとキャッチMOSFETには、どちらもインダクタ電流の可能最大ピーク値より高いピーク・パルス定格電流が必要です。この可能最大ピーク値が生じるのは最大負荷電流時であり、次の式と等しくなります。

$$I_{LOAD(MAX)} + \frac{I_{RIPP(P-P)}}{2}$$

#### 3.V<sub>GS</sub>の最大定格

「INTV<sub>CC</sub>のバイアス電源」セクションで以前説明したように、INTV<sub>CC</sub>はLT8311によって内部で7Vに安定化されています。拡大解釈すると、LT8311の内部LDOを使用してINTV<sub>CC</sub>を安定化する場合、キャッチMOSFETおよびフォワードMOSFETのゲートは最大7Vまで駆動できます。LT8311の内部LDOを使用するアプリケーションでは、V<sub>GS</sub>の最大値が10Vより高いMOSFETを選択すれば十分です。

LINEAR

一方、 $INTV_{CC}$ ピンは外部で最大16Vまでオーバードライブできます。こうしたアプリケーションでは、 $V_{GS}$ の最大値が $\pm 20V$ のMOSFETを選択すれば十分です。

#### 4.R<sub>DS(ON)</sub>によるMOSFETの損失の計算

キャッチ MOSFET とフォワード MOSFET に付随する導通損失/抵抗損は、MOSFET の RMS 電流とそのオン抵抗の関数です。大半のフォワード・コンバータ・アプリケーションは、通常は出力の最大負荷電流が大きい(5A以上)ので、MOSFET の RDS(ON)に付随する損失を最小限に抑えることの方が、MOSFET のゲート電荷に付随する損失を最小限に抑えることよりはるかに重要になります。

キャッチ MOSFET の抵抗損 = (I<sub>CAT\_RMS</sub>)<sup>2</sup> • R<sub>CAT</sub>

ここで、R<sub>CAT</sub>はキャッチ MOSFET のオン抵抗(R<sub>DS(ON)</sub>)です。

フォワード MOSFET の抵抗損 = (I<sub>FWD\_RMS</sub>)<sup>2</sup> • R<sub>FWD</sub>

ここで、R<sub>FWD</sub>はフォワード MOSFET のオン抵抗(R<sub>DS(ON)</sub>)です。

## 5.Qqベースの損失の計算

2次側の同期 MOSFET に付随するゲート電荷  $(Q_g)$  ベースの損失には、以下の2つの側面があります。

#### A. Q<sub>a</sub>ベースのMOSFETスイッチング損失:

キャッチMOSFETがオン/オフするタイミングは、プリアクティブ・モードか同期モードかにかかわらず、ZVS (ゼロ電圧切り替え)時です。キャッチMOSFETはオンするのは、インダクタ電流がMOSFETのボディ・ダイオードを既に流れている後です。同様に、キャッチMOSFETがオフすると、インダクタ電流はその後にMOSFETのボディ・ダイオードを流れます。その結果、スイッチング時のキャッチMOSFETのドレイン-ソース端子間電圧は小さくなり、キャッチMOSFETのスイッチング損失はわずかなものになります。

フォワードMOSFETがオン/オフするタイミングは、プリアクティブ・モードか同期モードにかかわらず、それぞれZVS(ゼロ電圧切り替え)時およびZCS(ゼロ電流切り替え)時です。フォワードMOSFETがオンするのは、トランスのリセットが完了した後です。トランスのリセット完了は、フォワードMOSFETのボディ・ダイオードを流れるトランスの磁化電流が目印になります。これにより、フォワードMOSFETに小さなドレイン・ソース間電圧を加えることでフォワードMOSFETをオンすることができます。同様に、フォワードMOSFETがオフするのは、通常は1次側MOSFETがオフした後です。1次側MOSFETがオフすると、フォワードMOSFETが流れる唯一の電流がトランス磁化電流となりますが、この電流は事実上0とみなすことができます。したがって、フォワードMOSFETのスイッチング損失はわずかです。

#### B. Qqベースのコンバータ電力損失:

「INTV<sub>CC</sub>のバイアス電源」セクションで以前説明したように、キャッチMOSFET およびフォワードMOSFET のオン/オフ時に発生した電力損失があり、これらのMOSFET のゲートへのゲート電荷 ( $Q_g$ ) の供給と関連しています。この電荷の供給元は、内部LDOを使用してINTV<sub>CC</sub>を安定化する場合はLT8311の $V_{IN}$ ピンに接続されている電源電圧であり、LT8311のINTV<sub>CC</sub>ピンを外部から駆動する場合はINTV<sub>CC</sub>ピンに接続されている電源電圧です。いずれの場合も、ゲート電荷の供給に関連した全損失は次のとおりです。

ここで、 $V_{SUPP}$ は、 $INTV_{CC}$ が内部で安定化されている場合、LT8311の $V_{IN}$ ピンに接続されている電源電圧です。あるいは、LT8311の $INTV_{CC}$ が外部から駆動されている場合、 $V_{SUPP}$ は $INTV_{CC}$ ピンに接続されている電源電圧です。 $Q_{gCAT}$ および $Q_{gFWD}$ は、それぞれキャッチMOSFETおよびフォワードMOSFETのゲート電荷 $(Q_g)$ です。 $f_{SW}$ はフォワード・コンバータのスイッチング周波数です。

#### プリアクティブ・モードでの RTIMER の設定

プリアクティブ・モードでは、タイムアウト期間が始まるまでに2つのCSW立ち上がりエッジの間に経過できる最大期間をTIMERピンの抵抗(R<sub>TIMER</sub>)によって設定します。タイムアウトにより、1次側ICがスイッチングを停止した場合、LT8311はすべての同期動作を停止できます。CSW立ち上がりエッジは1次側のスイッチング動作を表わすので、CSW立ち上がりエッジのタイムアウトはスイッチングの停止と解釈されます。その時点でLT8311は2次側同期スイッチングをすべて停止して、その評価期間を開始します。評価期間の詳細については、「動作」セクションを参照してください。評価期間内の条件がすべて満たされると、2次側のスイッチングは再開します。また、タイムアウトでは、プリアクティブ・モード内でのスイッチング動作が行われるのが、プリアクティブ・モードの動作周波数範囲内の周波数になることも保証されます。

図18に示すように、CSWピンの電圧が-150mVより低い電 圧レベルから上昇して1.2Vを超えるのを検出するたびに、 LT8311 はその内部タイムアウト信号をリセットします。キャッチ MOSFETのゲートであるCGは、CSWの電圧が-150mVより 低い電圧に低下するのを検出すると、(ある一定の伝播遅延 後に)オンします。CGが"H"になると、キャッチMOSFETがオ ンして、そのドレイン電圧(CSW)は(GNDに接続されている) ソース電圧の近くまで低下します。CGは、予想されるCSW立 ち上がりエッジの前にCCMで予測してオフします。(-150mV より低い電圧から1.2Vより高い電圧に上昇する) CSW 立ち 上がりエッジが、タイムアウト信号をリセットする時間内に出現 しない場合は、タイムアウト信号によって最終的に電圧VRFF TIMEOUTまで充電され、内部タイムアウト状態が生じます。そ の結果、LT8311は同期式の導通をすべて停止し、評価期間 を開始します。評価期間が終了するのは、内部タイムアウト信 号が適切なタイミングでリセットするなど、「動作」セクションに 示す4つの条件が、連続3回のCSW立ち上がりエッジで満た される場合に限ります。評価期間が完了すると、LT8311は同 期制御を再開します。

図18. プリアクティブ・モードでタイムアウトが発生すると、LT8311は同期式の導通をすべて停止し、 評価期間を開始する(注記: CSW のリンギング波形が生じるのは、インダクタ電流が OA になることが原因)。

LINEAR

TIMERの抵抗は、通常はフォワード・コンバータの公称のスイッチング周期より20%長いタイムアウト期間を設定するよう選択します。

$$Timeout = \frac{1.20}{f_{SW}}$$

ここで、fsw はコンバータのスイッチング周波数(Hz)です。

タイムアウト期間を一度計算すれば、TIMERピンの抵抗 (R<sub>TIMER</sub>)は以下のように計算できます。

R<sub>TIMER</sub> (kΩ) ~ 22.1E6 • Timeout

ここで、Timeoutの単位は秒です。

R<sub>TIMER</sub>とタイムアウトの関係は完全に線形ではありません。 標準的な一連のフォワード・コンバータ・スイッチング周波数 に対するR<sub>TIMER</sub>の値(最も近い1%精度抵抗)を表1に示し ます。

表1. さまざまなフォワード・コンバータ・ スイッチング周波数に対する1%精度のR<sub>TIMER</sub>抵抗値

| スイッチング周波数<br>(kHz) | タイムアウト (μs) = 1.2/fSW | RTIMER (kΩ) |

|--------------------|-----------------------|-------------|

| 100                | 12                    | 267         |

| 150                | 8                     | 178         |

| 200                | 6                     | 133         |

| 250                | 4.8                   | 107         |

| 300                | 4                     | 88.7        |

| 400                | 3                     | 66.5        |

| 500                | 2.4                   | 53.6        |

タイムアウト期間をスイッチング周期の1.2 倍に設定すると、スイッチング周波数がその最終値の80%に近づくまで、プリアクティブ・モードでの周波数フォールドバックによって同期式の導通は停止したままになります。このことは、スイッチング周波数が100kHzのアプリケーションでは、80kHzのときにLT8311がプリアクティブ・モードで同期式の導通が可能な状態であることを意味します。LT8311のデータシート規格では、80kHzはプリアクティブ・モードの動作周波数範囲外ですが、このデバイスは80kHzまで動作して、こうした周波数フォールドバック状態を乗り切る設計になっています。また、タイムアウトが生じると、軽出力負荷電流でCSWパルススキップ状態の場合に同期式の導通が停止する場合もあります。

#### 同期モードでの RTIMER の設定

同期モードでは、タイムアウト期間の機能はプリアクティブ・モードと同様です。ただし、SYNCピンの電圧が-1.2Vより低くなるたびに、LT8311の内部タイムアウト信号がリセットされることが異なります。同期モードでのタイムアウト機能の目標は、キャッチMOSFETがオンのままの状態が長すぎて、危険なレベルの逆方向出力インダクタ電流が流れる(電流が出力コンデンサからキャッチMOSFETのドレインに向かって逆に流れる)場合、主にキャッチMOSFETのオン時間を制限することです。危険なレベルの逆方向出力インダクタ電流を構成する要素に関する詳細については、「同期モードでの電流検出コンパレータのCSP/CSN入力の構成」セクションを参照してください。

同期モードでは、タイムアウト期間を1次側ICの最長のスイッチング周期より20%長く設定します。通常、1次側ICの最長のスイッチング周期は最小の周波数フォールドバック周波数(fsw smallest)に一致します。

$$Timeout = \frac{1.2}{f_{SW SMALLEST}}$$

タイムアウト期間を一度計算すれば、TIMERピンの抵抗 (RTIMER) は以下のように計算できます。

$$R_{TIMER}(k\Omega) \sim 22.1E6 \bullet Timeout$$

ここで、Timeoutの単位は秒で、fsw\_smallestの単位はHzです。

# プリアクティブ・モードでの電流検出コンパレータの CSP/CSN 入力の構成

LT8311の差動入力電流検出コンパレータは、キャッチ MOSFETを流れる電流の情報をLT8311に与える目的で使用されます。CSPピンおよびCSNピンをキャッチMOSFET(M<sub>CG</sub>)のドレインおよびソースに直列抵抗を介してそれぞれ接続し、LT8311がM<sub>CG</sub>のドレイン-ソース間電圧を検出して、その電流について推論できるようにします。あるいは、CSPとCSNを、M<sub>CG</sub>のソースとグランドの間に接続した検出抵抗の両端に、直列抵抗を介して接続してもかまいません。「動作」セクションで以前説明したように、CSPピンとCSNピンはプリアクティブ・モードで構成し、キャッチMOSFETの電流がゼロになったと

83111

きにコンパレータが作動するようにします。電流コンパレータ は内部では66mVで作動し、CSPピンからは40µAが流れ出 すので、1.65kの1%精度抵抗をCSPとCSNの間に直列に接 続することにより、キャッチMOSFETの両端の電圧がほぼ0V のときにLT8311が作動できるようにする必要があります。電 流コンパレータには公称100nsの伝播遅延があるので、電流 コンパレータが作動してからキャッチMOSFETがオフするま でには約100nsの時間がかかることに注意してください。この 100nsの間、出力インダクタを流れる電流はキャッチMOSFET のドレインからソースの方向へ逆に流れることができます。 McGに負の電流が流れるのが望ましくない場合は、キャッチ MOSFETのソースからドレインの方向に正の電流が流れると きコンパレータが作動するようにCSPピンの直列抵抗を選択 できます。次の式を使用すると、CSPピンと直列に接続する抵 抗(RCSP)を、キャッチ MOSFET の作動電流の目標値(ITRIP) に合わせて計算できます。

$$R_{CSP} = \frac{66mV - I_{TRIP} \cdot R_{SNS}}{40uA}$$

ここで、 $R_{SNS}$ は、CSPピンとCSNピンがキャッチMOSFETのドレイン端子とソース端子にそれぞれ直接接続されている場合、キャッチMOSFETの $R_{DS(ON)}$ です。あるいは、CSP/CSNピンを検出抵抗の両端に直接接続した場合、 $R_{SNS}$ はキャッチMOSFETのソースでの検出抵抗になります。CSPピンと直列に接続する抵抗( $R_{CSP}$ )が決まったら、同じ抵抗をCSNピンと直列に接続します。

## 同期モードでの電流検出コンパレータの CSP/CSN 入力の構成

フォワード・コンバータをFCM (強制連続モード)で動作させる必要がある場合、LT8311は通常は同期モードで動作します。同期モードでは、LT8311は、1次側ICのSoutピンからパルス・トランスを介して、SYNCピンで同期制御信号を受信します。同期モードで、LT8311のキャッチMOSFETのドレインとソースにCSP/CSNピンをそれぞれ接続する目的は、軽負荷時に逆インダクタ電流が大量に流れすぎないようにキャッチMOSFETを保護することです。

与えられている以下のガイドライン $(ステップ1\sim5)$ に従って、キャッチMOSFETの適切な逆電流作動点 $(V_{TRIP})$ を求めることができます。

**ステップ1**: 通常のFCM動作時でのワーストケースの負のインダクタ電流値を求めます。ワーストケースとなるのは、最小の周波数フォールドバック周波数、最高のV<sub>IN</sub>、0A負荷時の可能性が高いと思われます。この値を求める簡単な方法は、LT8311を同期モードで機能させ、CSP/CSNピンをGNDに短絡した状態でフォワード・コンバータを動作させることです。V<sub>IN</sub>を最大値、負荷を0Aに設定して起動時のインダクタ電流波形をオシロスコープで観察すると、正常な起動動作時にワーストケースの負のインダクタ電流値(I<sub>CATCH\_FET</sub>)を素早く求めることができます。これにより、CSP/CSN作動点の下限値(V<sub>TRIP</sub>の最小値)が設定されます。

VTRIPの最小値 = |ICATCH FET| • RDS(ON)

ここで、R<sub>DS(ON)</sub>はキャッチMOSFETのオン抵抗、I<sub>CATCH\_FET</sub>は起動時のFCM動作の期間に流れる負のインダクタ電流(キャッチMOSFETのドレインからソースに流れる電流)のワーストケースでの大きさです。

**<u>ステップ2</u>**:ステップ1で計算した値から一定の余裕を持たせる作動点(V<sub>TRIP</sub>)を選択します。標準的な余裕は20%であると考えられるので、次の作動点を設定します。

V<sub>TRIP</sub> = 1.2 • V<sub>TRIP</sub>の最小値

**ステップ3**: 選択したキャッチ MOSFET の単一パルス・アバランシェ・エネルギー定格 ( $E_{AS}$ 、単位:mJ)と、そのドレイン-ソース間ブレークダウン電圧 ( $V_{BR(DSS)}$ 、単位:V)をMOSFET のデータシートで調べます。

**ステップ4**:キャッチMOSFETがオフしたときに、そのアバランシェ・エネルギー定格(基準は次の式)を超えないように、選択したCSP/CSN作動電圧では、キャッチMOSFETにあまり多くの負電流が流れないことを確認してください。

$$V_{TRIP}$$

(in Volts)  $< R_{DS(ON)} \bullet$

$$\sqrt{\left[2 \bullet \mathsf{E}_{\mathsf{AS}} \bullet \frac{(1.3 \bullet \mathsf{V}_{\mathsf{BR}(\mathsf{DSS})} - \mathsf{V}_{\mathsf{OUT}})}{(1.3 \bullet \mathsf{V}_{\mathsf{BR}(\mathsf{DSS})} \bullet \mathsf{L}_{\mathsf{OUT}})}\right]}$$

ここで、

$E_{AS}$ (ジュール) = キャッチ MOSFET の単一パルス・アバランシェ・エネルギー定格。

$V_{BR(DSS)}(V) = キャッチMOSFETのドレイン-ソース間ブレークダウン電圧定格。$

/ LINEAR

## アプリケーション情報

$R_{DS(ON)}(\Omega) = キャッチMOSFETのデータシートで調べた MOSFETのオン抵抗定格。$

VOLT(V)=フォワード・コンバータの定常状態での出力電圧。

$L_{OUT}(H) = 出力インダクタ。$

V<sub>TRIP</sub>の電圧が大きすぎるとキャッチMOSFETのアバランシェ・エネルギー定格を超えるので、その場合はステップ1および2に戻って、このアプリケーションでMOSFETが受けるアバランシェ・エネルギーがデータシートに規定されたSOAの範囲内に収まるまで調整するか、別のMOSFETを選択します。

ステップ5: 適切な作動点を選択するときに、直列抵抗(R<sub>CSP</sub> およびR<sub>CSN</sub>)を次の式に基づいて決定することができます。

$$R_{CSP} = R_{CSN} = \frac{66mV - V_{TRIP}}{40\mu A}$$

CSPピンとキャッチMOSFETのドレインの間にR<sub>CSP</sub>を接続し、 CSNピンとキャッチMOSFETのソースの間にR<sub>CSN</sub>を接続し ます。

## プリアクティブ・モードの同期制御

#### プリアクティブ・モードの一般的ガイドライン

次のガイドラインは、LT8311の同期制御をプリアクティブ・モードで準備するために一般的に必要となる接続および動作条件の概要を示すのが目的です。これらのガイドラインは出発点として役立つことを想定していますが、ベンチ評価の代わりにはなりません。LT8311のプリアクティブ・モード方式を使用する各アプリケーションは、最終的にはその特定要件について評価する必要があり、デバイスはそれに応じて構成する必要があります。

- 1. データシートの推奨事項に従って $V_{IN}$ と $INTV_{CC}$ にバイアスをかけます。

- 2.  $V_{IN}$ ピンとGNDの間に2.2 $\mu$ F以上のセラミック・コンデンサを接続します。

- 3.  $INTV_{CC}$ ピンとGNDの間に $4.7\mu$ F以上のセラミック・コンデンサを接続します。

- 4. PMODE ピンとSYNCピンを0Vに接続します。

- 5. R<sub>TIMER</sub>を配置して、フォワード・コンバータの定常状態のスイッチング周期より20%長いタイムアウト期間を設定します。

- 6. CSWピンとFSWピンを、2kのセラミック抵抗を介して、 キャッチMOSFETおよびフォワードMOSFETのドレイン にそれぞれ接続します。接続の長さはできるだけ短くしてく ださい。

- 7. V<sub>DS</sub>を検出するために、キャッチ MOSFET のドレイン端子とソース端子に、1.65kの抵抗を介して CSP ピンと CSN ピンをそれぞれ直接接続します。内部で結合する外部ノイズを除去するために、 CSP ピンと CSN ピンの間に小型の10pFフィルタ・コンデンサが必要な場合があります。

- 8. キャッチMOSFETおよびフォワードMOSFETのゲートに、 CGとFGをそれぞれできるだけ短い距離で接続します。

同期制御が動作状態になったら、以下のガイドラインに従います。

- 9. CSWピンとFSWピンの電圧が150Vの絶対最大定格を超えないことを確認します。CSWピンまたはFSWピンの電圧が150Vを超える場合は、キャッチMOSFETまたはフォワードMOSFET(あるいはその両方)のドレインにRCスナバ回路を使用することが必要になる可能性があります。

- 10. キャッチMOSFET電流の作動点によって軽負荷時にインダクタ電流が逆方向に流れる(出力からキャッチMOSFETのドレインに戻る)場合は、CSP/CSNの作動点を再設定して、キャッチMOSFETのソース-ドレイン間電流がわずかに正の値になったときに(内部コンパレータが)作動するようにします。こうするには、通常はCSPとCSNに接続する直列抵抗を1.65kより大きい値に増加することが必要です。

- 11. キャッチ MOSFET の電流の作動点が一貫しているように 見えず、キャッチ MOSFET のターンオフ・エッジが作動電 流時にジッタを示すように見える場合、CSPピンとCSNピンの間のフィルタ・コンデンサを調整することが必要にな る可能性があります。

電圧帰還ループの一部としてLT8311を使用する場合、通常は、FBピンを抵抗分割器回路網を介して出力電圧に接続することに注意してください。

83111

## アプリケーション情報

#### 同期モードの同期制御

### パルス・トランスと高域通過フィルタの選択

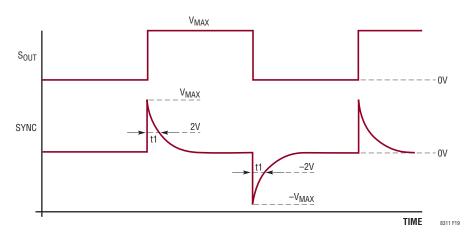

同期モードでは、LT8311は、キャッチMOSFETおよびフォワードMOSFETのオン/オフのタイミングをSYNCピンの電圧信号に基づいて決定します。1次側ICのSOUTピンからLT8311のSYNCピンに同期制御信号を伝達するために使用する標準的な回路を、「動作」セクションの図7に示します。この回路では、1次側と2次側の間の絶縁を実現するパルス・トランス(図7ではT2)と、高域通過フィルタ(RSYNCおよびCSYNC)を使用します。CSYNCは、DC信号がT2に直接加わるのを遮断します。高域通過フィルタ(RSYNCおよびCSYNC)によってSOUT信号のDC成分を除去すると、図19に示すように、SOUTの立ち上がりエッジおよび立ち下がりエッジでSYNCピンの信号を正または負にすることができます。正負の信号の大きさと期間が等しいと、トランスT2での正と負のボルト秒を等しく維持できるので、磁化電流の正味の増加を防止できます。

R<sub>SYNC</sub>とC<sub>SYNC</sub>の値を適切に選択して、以下の基準をすべて満たす必要があります。

1. 十分なオーバードライブ電圧により、SYNCピンに十分長いパルス幅を生成できるように、R<sub>SYNC</sub>・C<sub>SYNC</sub>時定数は十分に大きくする必要があります。これを図19に示します。ここで、SYNCピンの電圧が±2V(以上のオーバードライブ)のときt1を50ns以上にして、SYNCコンパレータを作動させる必要があります。この制約条件を適用することにより、次の式ではR<sub>SYNC</sub>・C<sub>SYNC</sub>の積に要求される最小値に関して制限値が設定されます。

$$R_{SYNC} \cdot C_{SYNC} \ge \frac{50ns}{\left[-1 \cdot \ell n \left(\frac{2V}{V_{MAX}}\right)\right]}$$

ここで、 $V_{MAX}$ は、図19に示すように $S_{OUT}$ の最大電圧です。

2. R<sub>SYNC</sub>は十分に小さくして、SYNC信号が十分に減衰することを保証する必要があります。SYNC信号の減衰が不足すると、SYNC検出コンパレータが誤作動する原因になるほどリンギングが大きくなって、2次側の同期制御が不適切になる可能性があります。最適な減衰を実現するためのR<sub>SYNC</sub>を計算するのに使用する式は、次のとおりです。

$$R_{SYNC} \leq \left(\frac{1}{2 \bullet \zeta}\right) \bullet \sqrt{\frac{L_m}{C_{SYNC}}}$$

ここでζは減衰率で、通常は約1になるように選択します。 Lmはパルス・トランスの1次巻線の磁化インダクタンスです。

大きなLmを選択すると減衰率を高くすることができるので、1次巻線インダクタンスの大きいパルス・トランスを選択してSYNC信号の減衰量を増やすのが賢明です。

また、R<sub>SYNC</sub>の値を小さくした場合も、内部で結合する可能性がある漂遊信号(寄生磁界)に対する高域通過フィルタの感度が低下します。

図19. SYNC信号の正と負のエッジは、それぞれ S<sub>OUT</sub>の立ち上がりエッジおよび立ち下がりエッジで生成される。LT8311 は、 SYNCピンの電圧が±2V(以上のオーバードライブ)のときパルス幅の時間t1を50ns(標準)以上にして、 内部のSYNC検出コンパレータを作動させることが必要。

LINEAD TECHNOLOGY

8311f

# アプリケーション情報

3. R<sub>SYNC</sub>の値は、正または負のSYNCピン電圧信号が発生するたびに、必要なソース/シンク電流の量を制限するのに十分なほど大きくなければなりません。S<sub>OUT</sub>ピンのゲート・ドライバのソース電流供給能力は限られているので、R<sub>SYNC</sub>を十分に大きくして、電流駆動時にこの制約条件に違反しないようにする必要があります。たとえば、LT3752のS<sub>OUT</sub>ドライバの最大電流定格は約100mAです。この結果、次のようになります。

$$R_{SYNC} \ge \frac{V_{MAX}}{100mA}$$

$V_{MAX}$ は $S_{OUT}$ ゲート・ドライバの"H"電圧で、LT3752の場合は標準で約 $8V \sim 12V$ です。

以下の手順をガイドラインとして使用して、 $R_{SYNC}$ と $C_{SYNC}$ の値を計算できます。

<u>ステップ</u>1:パルス・トランスを選択します。標準的な推奨品は Pulse Electronics 製の PE-68386NLです。

**ステップ2**:1次側ICの $S_{OUT}$ の信号の最大振幅 $V_{MAX}$ を決めます(図19参照)。これにより、LT8311のSYNCピンの信号の最大振幅が設定されます。

**ステップ3**:  $C_{SYNC}$ の容量値を推測します。初期値として適切な範囲は220F~1nFと考えられます。

**ステップ4**:次の式に示す制約条件に基づいてR<sub>SYNC</sub>を選択します。

$$\begin{split} &\frac{1}{2} \bullet \sqrt{\left(\frac{L_{m}}{C_{SYNC}}\right)} \geq R_{SYNC} \geq MAX \\ &\left\{ \frac{50 ns}{\left[C_{SYNC} \bullet -1 \bullet IN(2V / V_{MAX})\right]} \right., \left. \left(\frac{V_{MAX}}{I_{MAX}}\right) \right\} \end{split}$$

ここでI<sub>MAX</sub>は、1次側ICのS<sub>OUT</sub>ピンの最大電流ソース/シンク能力です(LT3752の最大電流能力は約100mAであり、LT8310の最大電流能力は約300mAです)。I<sub>MAX</sub>を規定の最大推奨ソース電流より小さい値に設計して、プロセスと温度に対する設計余裕を考慮に入れることを推奨します。

ステップ4の $R_{SYNC}$ の計算結果が不合理な抵抗値になる場合は、ステップ $1\sim3$ に戻って、 $L_m$ 、 $V_{MAX}$ 、 $C_{SYNC}$ のいずれかを変更してください。すべての基準が満たされるまで、ステップ4で $R_{SYNC}$ を再計算します。

#### 設計例

LT3752-LT8311のフォワード・コンバータ設計では、パルス・トランスPE-68386NLを選択し、LT3752のS<sub>OUT</sub>信号を高域通過フィルタを通してからLT8311のSYNCピンに伝達しています。

ステップ1:このトランスの磁化インダクタンスLmは785µHです。

ステップ2:LT3752の $V_{MAX}$ は12Vです。

ステップ3:C<sub>SYNC</sub>には220pFを選択します。

**ステップ 4:**  $I_{MAX}$  = 70mA、 $L_m$  = 785 $\mu$ H、 $C_{SYNC}$  = 220pF、 $V_{MAX}$  = 12Vに合わせて設計すると、 $R_{SYNC}$ について次の計算結果が得られます。

$944\Omega \ge R_{SYNC} \ge Max \{127\Omega, 171\Omega\}$

#### まとめ

この例では、パルス・トランスPE-68386NLと組み合わせて使用する高域通過フィルタとして $R_{SYNC}$  =  $560\Omega$ と $C_{SYNC}$  = 220pFを選択して、LT3752の $S_{OUT}$ 信号をLT8311のSYNCピンに伝達しています。

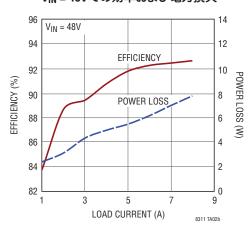

### 18V~72V入力、12V/8A出力のアクティブ・クランプ絶縁型フォワード・コンバータ

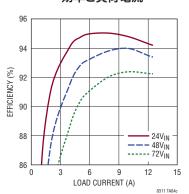

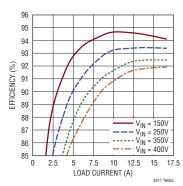

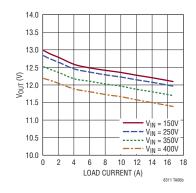

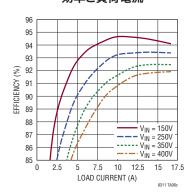

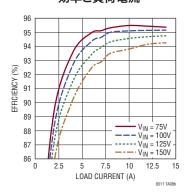

### VIN = 48Vでの効率および電力損失

CENTRAL SEMI. CMMR1U-02

DIODES INC. SBRIU150

D2:

### 18V~72V入力、12V/12.5A、150W出力のアクティブ・クランプ絶縁型フォワード・コンバータ

###

### 18V~72V入力、12V/12.5A、150W出力、オプトカプラ不要のアクティブ・クランプ絶縁型フォワード・コンバータ

- T1: CHAMPS G45R2\_0404.04D

- T2: BH ELECTRONICS L00-3250 T3: PULSE PE-68386NL

- L1: CHAMPS G45AH2-0404-D4 D1, D2, D3: BAS516

- D4: CENTRAL SEMI CMMR1U-02

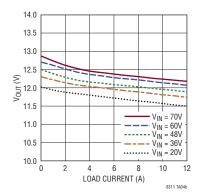

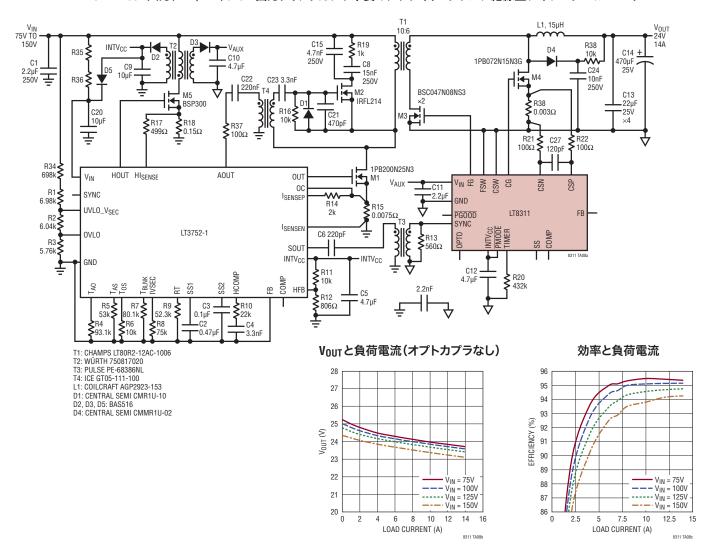

## Voutと負荷電流(オプトカプラなし)

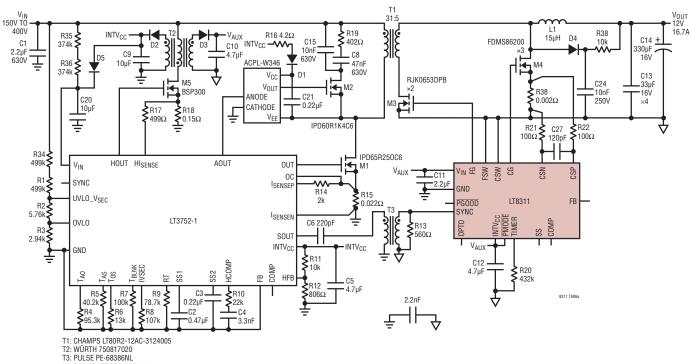

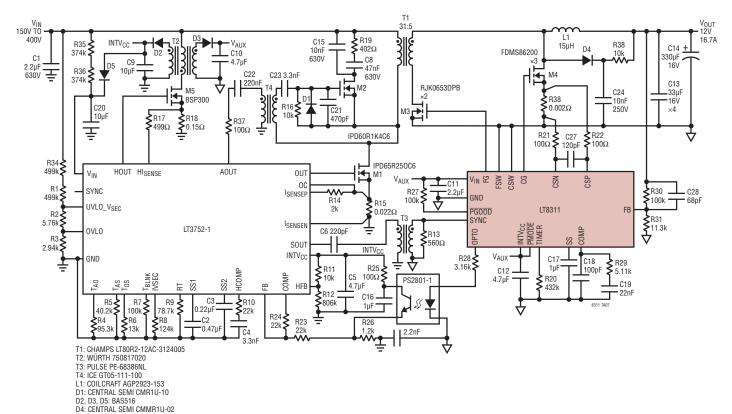

#### 150V~400V入力、12V/16.7A、200W出力のアクティブ・クランプ絶縁型フォワード・コンバータ

150V~400V入力、12V/16.7A、200W出力、オプトカプラ不要のアクティブ・クランプ絶縁型フォワード・コンバータ

- L1: COILCRAFT AGP2923-153 D1: CENTRAL SEMI CMR1U-10

- D2, D3, D5: BAS516 D4: CENTRAL SEMI CMMR1U-02

### Vout と負荷電流(オプトカプラなし)

### 150V~400V入力、12V/16.7A、200W出力のアクティブ・クランプ絶縁型フォワード・コンバータ (高電位側アクティブ・クランプにゲート駆動トランスを使用)

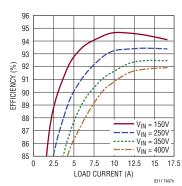

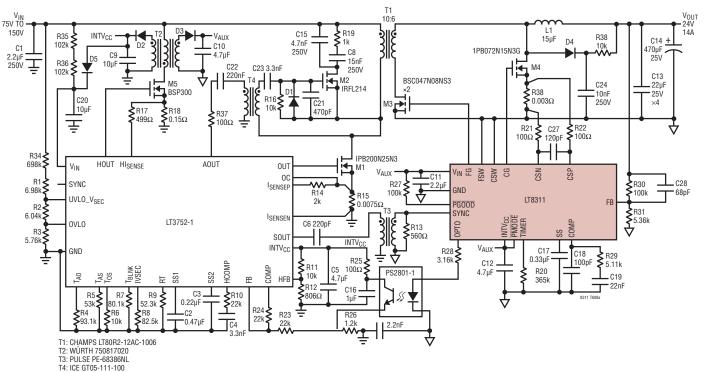

### 75V~150V入力、24V/14A、340W出力のアクティブ・クランプ絶縁型フォワード・コンバータ (高電位側アクティブ・クランプにゲート駆動トランスを使用)

- L1: COILCRAFT AGP2923-153 D1: CENTRAL SEMI CMR1U-10

- D2, D3, D5: BAS516 D4: CENTRAL SEMI CMMR1U-02

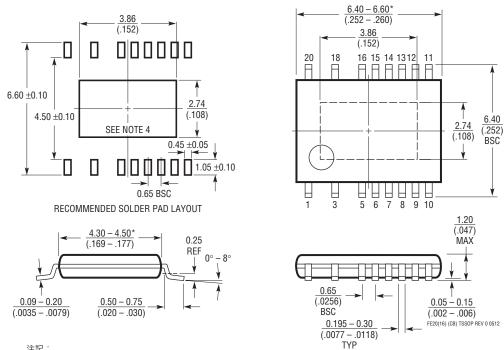

## パッケージ

最新のパッケージ図面については、http://www.linear-tech.co.jp/designtools/packaging/を参照してください。

### FE Package Variation: FEŽO(16) 20-Lead Plastic TSSOP (4.4mm)

(Reference LTC DWG # 05-08-1924 Rev Ø)

### **Exposed Pad Variation CB**

- 注記:

- 1. 標準寸法: ミリメートル

- 2. 寸法は <u>ミリメートル</u> (インチ)

- 3. 図は実寸とは異なる

- 4. 露出パッド接着のための推奨最小 PCB メタルサイズ

- \* 寸法にはモールドのバリを含まない。

- モールドのバリは各サイドで 0.150mm (0.006")を超えないこと

#### 75V~150V入力、24V/14A、340W出力、オプトカプラ不要のアクティブ・クランプ絶縁型フォワード・コンバータ

# 関連製品

| 製品番号                    | 説明                                                      | 注釈                                                        |

|-------------------------|---------------------------------------------------------|-----------------------------------------------------------|

| LT3752/LT3752-1         | ハウスキーピング・コントローラを内蔵した<br>アクティブ・クランプ同期整流式フォワード・<br>コントローラ | 中電力の24V、48Vおよび最大400V入力アプリケーションに最適                         |

| LT3753                  | 100V 入力のアクティブ・クランプ同期整流式<br>フォワード・コントローラ                 | 中電力の24Vおよび48V入力アプリケーションに最適                                |

| LTC3765/LTC3766         | オプトカプラ不要の絶縁型同期整流式フォワード・<br>コントローラ・チップセット                | Direct Flux Limit、マルチフェーズ対応により、中電力の24Vおよび48V入力アプリケーションに最適 |

| LTC3722-1/<br>LTC3722-2 | 同期整流式位相変調フルブリッジ・コントローラ                                  | 高電力の24V および48V 入力アプリケーションに最適                              |

| LT3748                  | 絶縁型フライバック・コントローラ                                        | $5V \le V_{IN} \le 100V$ 、オプトカプラ不要のMSOP-16(12)            |

| LT8300                  | 100Vマイクロパワー絶縁型フライバック・コンバータ                              | モノリシック、オプトカプラ不要、260mAスイッチ内蔵、TSOT-23                       |